pdf (90) - Faculdade de Informática - pucrs

pdf (90) - Faculdade de Informática - pucrs

pdf (90) - Faculdade de Informática - pucrs

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Cada FPGA da família Virtex possui CLBs, IOBs, blocos <strong>de</strong> RAM, recursos <strong>de</strong> relógio, roteamen-<br />

to programável e configuração do circuito elétrico. Essas funcionalida<strong>de</strong>s lógicas são <strong>de</strong>terminadas<br />

através <strong>de</strong> um arquivo <strong>de</strong> configuração. Arquivos <strong>de</strong> configuração contêm uma mescla <strong>de</strong> comandos<br />

e dados. Eles po<strong>de</strong>m ser lidos e escritos através <strong>de</strong> uma das interfaces <strong>de</strong> configuração da Virtex.<br />

A memória <strong>de</strong> configuração da Virtex po<strong>de</strong> ser vista como uma matriz bidimensional <strong>de</strong> bits. Es-<br />

tes bits são agrupados em quadros verticais com um bit <strong>de</strong> largura, e se esten<strong>de</strong>m do topo à base da ma-<br />

triz. Um quadro é a unida<strong>de</strong> atômica <strong>de</strong> configuração: é a menor porção <strong>de</strong> memória <strong>de</strong> configura-<br />

ção que po<strong>de</strong> ser lida ou escrita.<br />

Quadros são lidos e escritos seqüencialmente, com en<strong>de</strong>reços crescentes para cada operação. Múl-<br />

tiplos quadros consecutivos po<strong>de</strong>m ser lidos ou escritos com um único comando <strong>de</strong> configuração. A<br />

matriz <strong>de</strong> CLBs inteira, mais o bloco <strong>de</strong> interconexão <strong>de</strong> SelectRAM po<strong>de</strong>m ser lidos ou escritos com<br />

apenas um comando. Cada bloco <strong>de</strong> conteúdo <strong>de</strong> SelectRAM <strong>de</strong>ve ser lido ou escrito separadamente.<br />

Como os quadros po<strong>de</strong>m ser lidos ou escritos individualmente, é possível reconfigurar parcialmen-<br />

te esses dispositivos através da modificação <strong>de</strong>sses quadros no arquivo <strong>de</strong> configuração. Além disto, a<br />

disposição regular <strong>de</strong> elementos permite ações <strong>de</strong> relocação e <strong>de</strong>sfragmentação, que são importantes<br />

para reconfiguração parcial [COM99].<br />

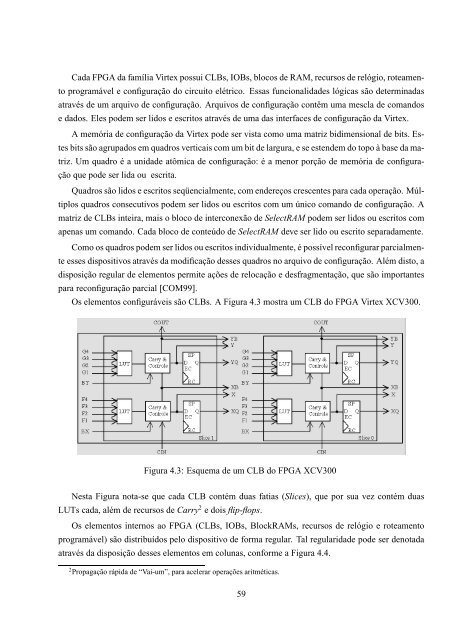

Os elementos configuráveis são CLBs. A Figura 4.3 mostra um CLB do FPGA Virtex XCV300.<br />

Figura 4.3: Esquema <strong>de</strong> um CLB do FPGA XCV300<br />

Nesta Figura nota-se que cada CLB contém duas fatias (Slices), que por sua vez contém duas<br />

LUTs cada, além <strong>de</strong> recursos <strong>de</strong> Carry 2 e dois flip-flops.<br />

Os elementos internos ao FPGA (CLBs, IOBs, BlockRAMs, recursos <strong>de</strong> relógio e roteamento<br />

programável) são distribuídos pelo dispositivo <strong>de</strong> forma regular. Tal regularida<strong>de</strong> po<strong>de</strong> ser <strong>de</strong>notada<br />

através da disposição <strong>de</strong>sses elementos em colunas, conforme a Figura 4.4.<br />

2 Propagação rápida <strong>de</strong> “Vai-um”, para acelerar operações aritméticas.<br />

59