pdf (90) - Faculdade de Informática - pucrs

pdf (90) - Faculdade de Informática - pucrs

pdf (90) - Faculdade de Informática - pucrs

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Barramentos Globais<br />

n<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

n<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

2<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

2 1<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

Registradores <strong>de</strong> Passagem<br />

EP EP EP EP<br />

EP<br />

Interconexão<br />

EP<br />

Interconexão<br />

EP<br />

1<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

EP<br />

0<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

0<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

Figura 2.11: Abstração da arquitetura PipeRench.<br />

Um<br />

Estágio<br />

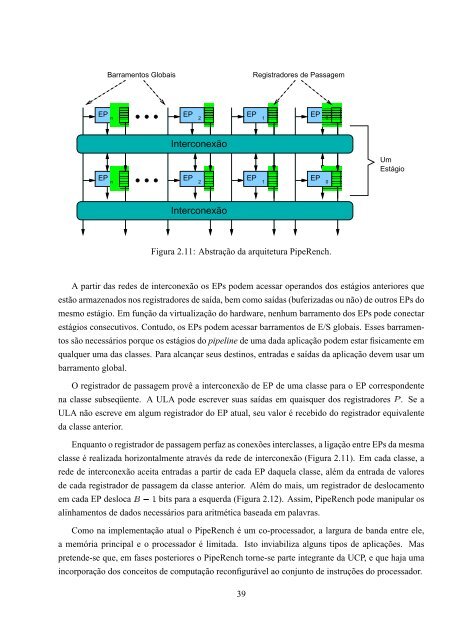

A partir das re<strong>de</strong>s <strong>de</strong> interconexão os EPs po<strong>de</strong>m acessar operandos dos estágios anteriores que<br />

estão armazenados nos registradores <strong>de</strong> saída, bem como saídas (buferizadas ou não) <strong>de</strong> outros EPs do<br />

mesmo estágio. Em função da virtualização do hardware, nenhum barramento dos EPs po<strong>de</strong> conectar<br />

estágios consecutivos. Contudo, os EPs po<strong>de</strong>m acessar barramentos <strong>de</strong> E/S globais. Esses barramen-<br />

tos são necessários porque os estágios do pipeline <strong>de</strong> uma dada aplicação po<strong>de</strong>m estar fisicamente em<br />

qualquer uma das classes. Para alcançar seus <strong>de</strong>stinos, entradas e saídas da aplicação <strong>de</strong>vem usar um<br />

barramento global.<br />

O registrador <strong>de</strong> passagem provê a interconexão <strong>de</strong> EP <strong>de</strong> uma classe para o EP correspon<strong>de</strong>nte<br />

na classe subseqüente. A ULA po<strong>de</strong> escrever suas saídas em quaisquer dos registradores . Se a<br />

ULA não escreve em algum registrador do EP atual, seu valor é recebido do registrador equivalente<br />

da classe anterior.<br />

Enquanto o registrador <strong>de</strong> passagem perfaz as conexões interclasses, a ligação entre EPs da mesma<br />

classe é realizada horizontalmente através da re<strong>de</strong> <strong>de</strong> interconexão (Figura 2.11). Em cada classe, a<br />

re<strong>de</strong> <strong>de</strong> interconexão aceita entradas a partir <strong>de</strong> cada EP daquela classe, além da entrada <strong>de</strong> valores<br />

<strong>de</strong> cada registrador <strong>de</strong> passagem da classe anterior. Além do mais, um registrador <strong>de</strong> <strong>de</strong>slocamento<br />

em cada EP <strong>de</strong>sloca bits para a esquerda (Figura 2.12). Assim, PipeRench po<strong>de</strong> manipular os<br />

alinhamentos <strong>de</strong> dados necessários para aritmética baseada em palavras.<br />

Como na implementação atual o PipeRench é um co-processador, a largura <strong>de</strong> banda entre ele,<br />

a memória principal e o processador é limitada. Isto inviabiliza alguns tipos <strong>de</strong> aplicações. Mas<br />

preten<strong>de</strong>-se que, em fases posteriores o PipeRench torne-se parte integrante da UCP, e que haja uma<br />

incorporação dos conceitos <strong>de</strong> computação reconfigurável ao conjunto <strong>de</strong> instruções do processador.<br />

39