SP - UMEL - Vysoké uÄÂenàtechnické v Brně

SP - UMEL - Vysoké uÄÂenàtechnické v Brně

SP - UMEL - Vysoké uÄÂenàtechnické v Brně

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

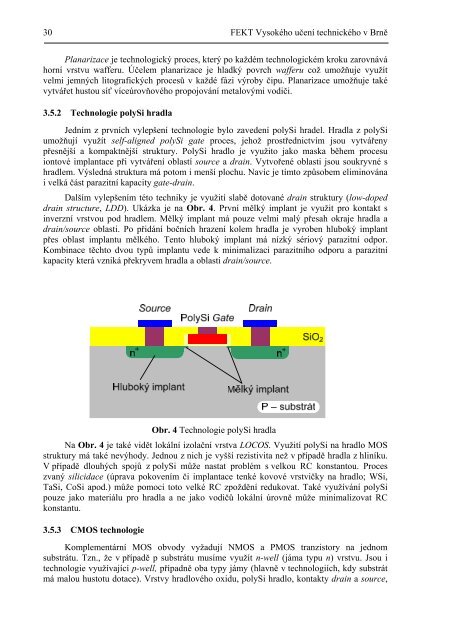

30 FEKT Vysokého učení technického v BrněPlanarizace je technologický proces, který po každém technologickém kroku zarovnáváhorní vrstvu wafferu. Účelem planarizace je hladký povrch wafferu což umožňuje využítvelmi jemných litografických procesů v každé fázi výroby čipu. Planarizace umožňuje takévytvářet hustou síť víceúrovňového propojování metalovými vodiči.3.5.2 Technologie polySi hradlaJedním z prvních vylepšení technologie bylo zavedení polySi hradel. Hradla z polySiumožňují využít self-aligned polySi gate proces, jehož prostřednictvím jsou vytvářenypřesnější a kompaktnější struktury. PolySi hradlo je využito jako maska během procesuiontové implantace při vytváření oblastí source a drain. Vytvořené oblasti jsou soukryvné shradlem. Výsledná struktura má potom i menší plochu. Navíc je tímto způsobem eliminovánai velká část parazitní kapacity gate-drain.Dalším vylepšením této techniky je využití slabě dotované drain struktury (low-dopeddrain structure, LDD). Ukázka je na Obr. 4. První mělký implant je využit pro kontakt sinverzní vrstvou pod hradlem. Mělký implant má pouze velmi malý přesah okraje hradla adrain/source oblasti. Po přidání bočních hrazení kolem hradla je vyroben hluboký implantpřes oblast implantu mělkého. Tento hluboký implant má nízký sériový parazitní odpor.Kombinace těchto dvou typů implantu vede k minimalizaci parazitního odporu a parazitníkapacity která vzniká překryvem hradla a oblasti drain/source.Obr. 4 Technologie polySi hradlaNa Obr. 4 je také vidět lokální izolační vrstva LOCOS. Využití polySi na hradlo MOSstruktury má také nevýhody. Jednou z nich je vyšší rezistivita než v případě hradla z hliníku.V případě dlouhých spojů z polySi může nastat problém s velkou RC konstantou. Proceszvaný silicidace (úprava pokovením či implantace tenké kovové vrstvičky na hradlo; WSi,TaSi, CoSi apod.) může pomoci toto velké RC zpoždění redukovat. Také využívání polySipouze jako materiálu pro hradla a ne jako vodičů lokální úrovně může minimalizovat RCkonstantu.3.5.3 CMOS technologieKomplementární MOS obvody vyžadují NMOS a PMOS tranzistory na jednomsubstrátu. Tzn., že v případě p substrátu musíme využít n-well (jáma typu n) vrstvu. Jsou itechnologie využívající p-well, případně oba typy jámy (hlavně v technologiích, kdy substrátmá malou hustotu dotace). Vrstvy hradlového oxidu, polySi hradlo, kontakty drain a source,