SP - UMEL - Vysoké uÄÂenàtechnické v Brně

SP - UMEL - Vysoké uÄÂenàtechnické v Brně

SP - UMEL - Vysoké uÄÂenàtechnické v Brně

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

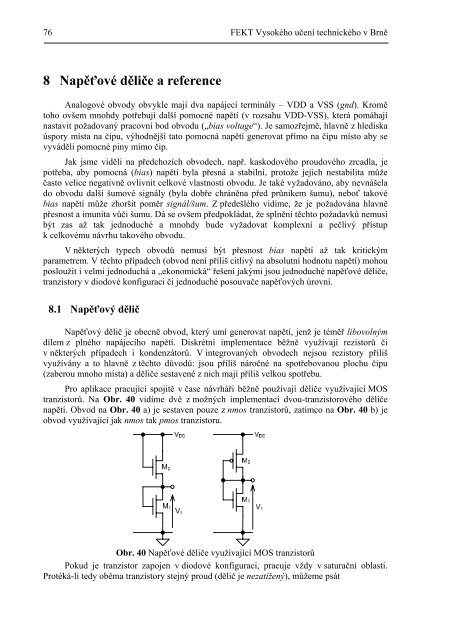

76 FEKT Vysokého učení technického v Brně8 Napěťové děliče a referenceAnalogové obvody obvykle mají dva napájecí terminály – VDD a VSS (gnd). Kromětoho ovšem mnohdy potřebují další pomocné napětí (v rozsahu VDD-VSS), která pomáhajínastavit požadovaný pracovní bod obvodu („bias voltage“). Je samozřejmě, hlavně z hlediskaúspory místa na čipu, výhodnější tato pomocná napětí generovat přímo na čipu místo aby sevyváděli pomocné piny mimo čip.Jak jsme viděli na předchozích obvodech, např. kaskodového proudového zrcadla, jepotřeba, aby pomocná (bias) napětí byla přesná a stabilní, protože jejich nestabilita můžečasto velice negativně ovlivnit celkové vlastnosti obvodu. Je také vyžadováno, aby nevnášelado obvodu další šumové signály (byla dobře chráněna před průnikem šumu), neboť takovébias napětí může zhoršit poměr signál/šum. Z předešlého vidíme, že je požadována hlavněpřesnost a imunita vůči šumu. Dá se ovšem předpokládat, že splnění těchto požadavků nemusíbýt zas až tak jednoduché a mnohdy bude vyžadovat komplexní a pečlivý přístupk celkovému návrhu takového obvodu.V některých typech obvodů nemusí být přesnost bias napětí až tak kritickýmparametrem. V těchto případech (obvod není příliš citlivý na absolutní hodnotu napětí) mohouposloužit i velmi jednoduchá a „ekonomická“ řešení jakými jsou jednoduché napěťové děliče,tranzistory v diodové konfiguraci či jednoduché posouvače napěťových úrovní.8.1 Napěťový děličNapěťový dělič je obecně obvod, který umí generovat napětí, jenž je téměř libovolnýmdílem z plného napájecího napětí. Diskrétní implementace běžně využívají rezistorů čiv některých případech i kondenzátorů. V integrovaných obvodech nejsou rezistory přílišvyužívány a to hlavně z těchto důvodů: jsou příliš náročné na spotřebovanou plochu čipu(zaberou mnoho místa) a děliče sestavené z nich mají příliš velkou spotřebu.Pro aplikace pracující spojitě v čase návrháři běžně používají děliče využívající MOStranzistorů. Na Obr. 40 vidíme dvě z možných implementací dvou-tranzistorového děličenapětí. Obvod na Obr. 40 a) je sestaven pouze z nmos tranzistorů, zatímco na Obr. 40 b) jeobvod využívající jak nmos tak pmos tranzistoru.Obr. 40 Napěťové děliče využívající MOS tranzistorůPokud je tranzistor zapojen v diodové konfiguraci, pracuje vždy v saturační oblasti.Protéká-li tedy oběma tranzistory stejný proud (dělič je nezatížený), můžeme psát