SP - UMEL - Vysoké uÄÂenàtechnické v Brně

SP - UMEL - Vysoké uÄÂenàtechnické v Brně

SP - UMEL - Vysoké uÄÂenàtechnické v Brně

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

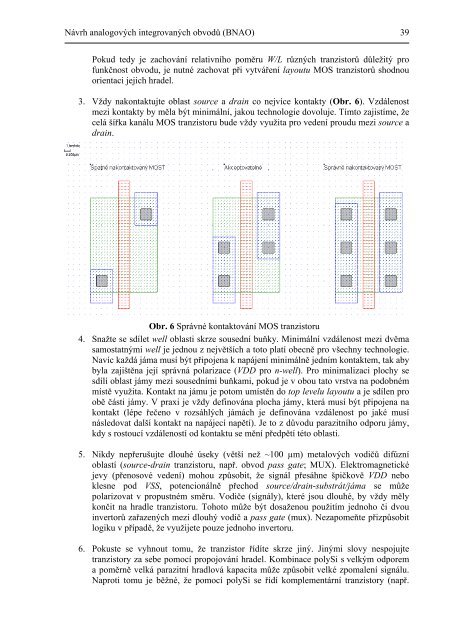

Návrh analogových integrovaných obvodů (BNAO) 39Pokud tedy je zachování relativního poměru W/L různých tranzistorů důležitý profunkčnost obvodu, je nutné zachovat při vytváření layoutu MOS tranzistorů shodnouorientaci jejich hradel.3. Vždy nakontaktujte oblast source a drain co nejvíce kontakty (Obr. 6). Vzdálenostmezi kontakty by měla být minimální, jakou technologie dovoluje. Tímto zajistíme, žecelá šířka kanálu MOS tranzistoru bude vždy využita pro vedení proudu mezi source adrain.Obr. 6 Správné kontaktování MOS tranzistoru4. Snažte se sdílet well oblasti skrze sousední buňky. Minimální vzdálenost mezi dvěmasamostatnými well je jednou z největších a toto platí obecně pro všechny technologie.Navíc každá jáma musí být připojena k napájení minimálně jedním kontaktem, tak abybyla zajištěna její správná polarizace (VDD pro n-well). Pro minimalizaci plochy sesdílí oblast jámy mezi sousedními buňkami, pokud je v obou tato vrstva na podobnémmístě využita. Kontakt na jámu je potom umístěn do top levelu layoutu a je sdílen proobě části jámy. V praxi je vždy definována plocha jámy, která musí být připojena nakontakt (lépe řečeno v rozsáhlých jámách je definována vzdálenost po jaké musínásledovat další kontakt na napájecí napětí). Je to z důvodu parazitního odporu jámy,kdy s rostoucí vzdáleností od kontaktu se mění předpětí této oblasti.5. Nikdy nepřerušujte dlouhé úseky (větší než ~100 µm) metalových vodičů difúzníoblastí (source-drain tranzistoru, např. obvod pass gate; MUX). Elektromagnetickéjevy (přenosové vedení) mohou způsobit, že signál přesáhne špičkově VDD neboklesne pod VSS, potencionálně přechod source/drain-substrát/jáma se můžepolarizovat v propustném směru. Vodiče (signály), které jsou dlouhé, by vždy mělykončit na hradle tranzistoru. Tohoto může být dosaženou použitím jednoho či dvouinvertorů zařazených mezi dlouhý vodič a pass gate (mux). Nezapomeňte přizpůsobitlogiku v případě, že využijete pouze jednoho invertoru.6. Pokuste se vyhnout tomu, že tranzistor řídíte skrze jiný. Jinými slovy nespojujtetranzistory za sebe pomocí propojování hradel. Kombinace polySi s velkým odporema poměrně velká parazitní hradlová kapacita může způsobit velké zpomalení signálu.Naproti tomu je běžné, že pomocí polySi se řídí komplementární tranzistory (např.