SP - UMEL - Vysoké uÄÂenàtechnické v Brně

SP - UMEL - Vysoké uÄÂenàtechnické v Brně

SP - UMEL - Vysoké uÄÂenàtechnické v Brně

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

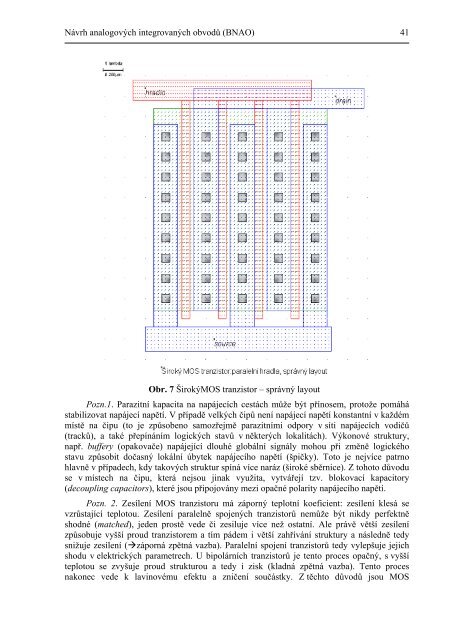

Návrh analogových integrovaných obvodů (BNAO) 41Obr. 7 ŠirokýMOS tranzistor – správný layoutPozn.1. Parazitní kapacita na napájecích cestách může být přínosem, protože pomáhástabilizovat napájecí napětí. V případě velkých čipů není napájecí napětí konstantní v každémmístě na čipu (to je způsobeno samozřejmě parazitními odpory v síti napájecích vodičů(tracků), a také přepínáním logických stavů v některých lokalitách). Výkonové struktury,např. buffery (opakovače) napájející dlouhé globální signály mohou při změně logickéhostavu způsobit dočasný lokální úbytek napájecího napětí (špičky). Toto je nejvíce patrnohlavně v případech, kdy takových struktur spíná více naráz (široké sběrnice). Z tohoto důvoduse v místech na čipu, která nejsou jinak využita, vytvářejí tzv. blokovací kapacitory(decoupling capacitors), které jsou připojovány mezi opačné polarity napájecího napětí.Pozn. 2. Zesílení MOS tranzistoru má záporný teplotní koeficient: zesílení klesá sevzrůstající teplotou. Zesílení paralelně spojených tranzistorů nemůže být nikdy perfektněshodné (matched), jeden prostě vede či zesiluje více než ostatní. Ale právě větší zesílenízpůsobuje vyšší proud tranzistorem a tím pádem i větší zahřívání struktury a následně tedysnižuje zesílení (záporná zpětná vazba). Paralelní spojení tranzistorů tedy vylepšuje jejichshodu v elektrických parametrech. U bipolárních tranzistorů je tento proces opačný, s vyššíteplotou se zvyšuje proud strukturou a tedy i zisk (kladná zpětná vazba). Tento procesnakonec vede k lavinovému efektu a zničení součástky. Z těchto důvodů jsou MOS