pdf-Datei mit 72-dpi-Fotos - FG Mikroelektronik, TU Berlin

pdf-Datei mit 72-dpi-Fotos - FG Mikroelektronik, TU Berlin

pdf-Datei mit 72-dpi-Fotos - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

Dissertation<br />

Perspektiven des modernen ASIC-Designs<br />

Kapitel 4.1<br />

Seite 40<br />

Schnittstellen selbst, nicht aber Details der Realisierung wie die interne Registerbelegung des<br />

Moduls, die Aufteilung von Funktionen zwischen Hardware und Software oder das Businterface<br />

zum Mikroprozessor, so dass hier viele Freiheiten verbleiben. Zur Integration eines IPs in das<br />

eigene System sind daher seitens der Software individuelle Treiber erforderlich, seitens des Businterfaces<br />

eine Anpassung des Moduls an das System oder die Konstruktion einer entsprechenden<br />

Umsetzlogik.<br />

Eine Standardisierung der Prozessorbusse könnte dieses Problem entschärfen, ist aber bis heute<br />

nicht erfolgreich realisiert worden, da verschiedene Mikroprozessorarchitekturen sowie firmenpolitische<br />

Entscheidungen eine herstellerübergreifende Normierung erschweren. Außerdem müssen<br />

bei der Definition eines Bussystems Kompromisse zwischen der Komplexität der<br />

Busfunktionen wie z. B. DMA- oder Multi-Master-Fähigkeit und der Zugriffsgeschwindigkeit<br />

eingegangen werden, was ebenfalls für individuell unterschiedliche Konzepte sprechen kann. Ein<br />

reines „Zusammenstecken“ von Mikroprozessor und IPs wird daher in den seltensten Fällen<br />

möglich sein.<br />

Die Vorteile für den ASIC-Designer bei der Wiederverwendung eigener Module sind offensichtlich;<br />

bei der Verwendung fremder IPs stellt sich jedoch die Frage, ob die Zeitersparnis den Kaufpreis<br />

rechtfertigt. Bei einer solchen Evaluierung wird der Wert eines IPs oft unterschätzt, indem<br />

nur die Entwicklungszeit für HDL-Codierung, Simulation und Debugging betrachtet wird und<br />

die nicht zu unterschätzende Einarbeitungszeit in die Spezifikation bzw. Norm der immer komplexeren<br />

Schnittstellen und Datenverarbeitungseinheiten vernachlässigt wird. Der Einsatz von<br />

IPs reduziert gerade die Spezifikationsphase auf ein absolutes Minimum und kann daher enorm<br />

zu einem sauberen Top-down-Design-Stil beitragen. Darüber hinaus werden die Risiken bei der<br />

Implementation bisher unbekannter Funktionen oft unterschätzt, die entfallen, wenn ein IP-Lieferant<br />

über eine Realisierung verfügt, die bereits erfolgreich in anderen ASICs oder Testchips ein-<br />

ISDN-S0<br />

S0<br />

S0<br />

S0 Interface<br />

(Switching Buffer)<br />

GPIO USB<br />

16 I/Os<br />

ISDN-S0<br />

USB V1.1<br />

2 Clk / 2 FSC / 4 PFS / 8 PCM-Hiway SDI/SDO<br />

PCMH<br />

clk + sync<br />

DTMF<br />

Decoder<br />

UART<br />

RS 232<br />

PCM<br />

Hiway<br />

High Speed Bus<br />

PCM<br />

Hiway<br />

PCM<br />

Hiway<br />

Software Switching Unit<br />

(Switching Buffer)<br />

Timer IRQ<br />

PLL<br />

(*8)<br />

12.288 MHz,<br />

48 MHz, Sysclk<br />

FSC PLL<br />

Int. Memory<br />

RAM / ROM<br />

Ext. Memory<br />

+<br />

SDRAM Ctrl.<br />

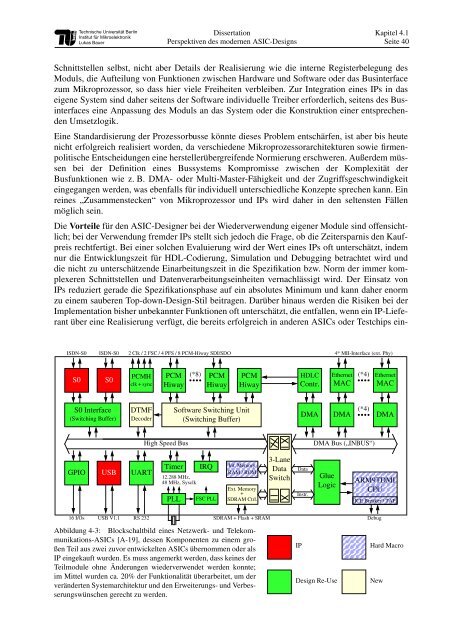

Abbildung 4-3: Blockschaltbild eines Netzwerk- und Telekommunikations-ASICs<br />

[A-19], dessen Komponenten zu einem großen<br />

Teil aus zwei zuvor entwickelten ASICs übernommen oder als<br />

IP eingekauft wurden. Es muss angemerkt werden, dass keines der<br />

Teilmodule ohne Änderungen wiederverwendet werden konnte;<br />

im Mittel wurden ca. 20% der Funktionalität überarbeitet, um der<br />

veränderten Systemarchitektur und den Erweiterungs- und Verbesserungswünschen<br />

gerecht zu werden.<br />

3-Lane<br />

Data<br />

Switch<br />

HDLC<br />

Contr.<br />

DMA<br />

Data<br />

Instr.<br />

4* MII-Interface (ext. Phy)<br />

Ethernet<br />

MAC<br />

DMA<br />

(*4)<br />

(*4)<br />

DMA Bus („INBUS“)<br />

Glue<br />

Logic<br />

Ethernet<br />

MAC<br />

DMA<br />

ARM9TDMI<br />

CPU<br />

ICE Breaker / TAP<br />

SDRAM + Flash + SRAM Debug<br />

IP<br />

Design Re-Use<br />

Hard Macro<br />

New