pdf-Datei mit 72-dpi-Fotos - FG Mikroelektronik, TU Berlin

pdf-Datei mit 72-dpi-Fotos - FG Mikroelektronik, TU Berlin

pdf-Datei mit 72-dpi-Fotos - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

Dissertation<br />

Perspektiven des modernen ASIC-Designs<br />

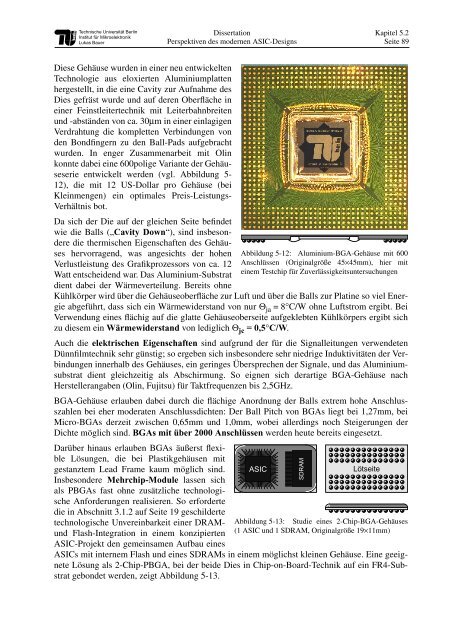

Diese Gehäuse wurden in einer neu entwickelten<br />

Technologie aus eloxierten Aluminiumplatten<br />

hergestellt, in die eine Cavity zur Aufnahme des<br />

Dies gefräst wurde und auf deren Oberfläche in<br />

einer Feinstleitertechnik <strong>mit</strong> Leiterbahnbreiten<br />

und -abständen von ca. 30μm in einer einlagigen<br />

Verdrahtung die kompletten Verbindungen von<br />

den Bondfingern zu den Ball-Pads aufgebracht<br />

wurden. In enger Zusammenarbeit <strong>mit</strong> Olin<br />

konnte dabei eine 600polige Variante der Gehäuseserie<br />

entwickelt werden (vgl. Abbildung 5-<br />

12), die <strong>mit</strong> 12 US-Dollar pro Gehäuse (bei<br />

Kleinmengen) ein optimales Preis-Leistungs-<br />

Verhältnis bot.<br />

Da sich der Die auf der gleichen Seite befindet<br />

wie die Balls („Cavity Down“), sind insbesondere<br />

die thermischen Eigenschaften des Gehäuses<br />

hervorragend, was angesichts der hohen<br />

Verlustleistung des Grafikprozessors von ca. 12<br />

Watt entscheidend war. Das Aluminium-Substrat<br />

dient dabei der Wärmeverteilung. Bereits ohne<br />

Kapitel 5.2<br />

Seite 89<br />

Kühlkörper wird über die Gehäuseoberfläche zur Luft und über die Balls zur Platine so viel Energie<br />

abgeführt, dass sich ein Wärmewiderstand von nur Θ ja = 8°C/W ohne Luftstrom ergibt. Bei<br />

Verwendung eines flächig auf die glatte Gehäuseoberseite aufgeklebten Kühlkörpers ergibt sich<br />

zu diesem ein Wärmewiderstand von lediglich Θ jc = 0,5°C/W.<br />

Auch die elektrischen Eigenschaften sind aufgrund der für die Signalleitungen verwendeten<br />

Dünnfilmtechnik sehr günstig; so ergeben sich insbesondere sehr niedrige Induktivitäten der Verbindungen<br />

innerhalb des Gehäuses, ein geringes Übersprechen der Signale, und das Aluminiumsubstrat<br />

dient gleichzeitig als Abschirmung. So eignen sich derartige BGA-Gehäuse nach<br />

Herstellerangaben (Olin, Fujitsu) für Taktfrequenzen bis 2,5GHz.<br />

BGA-Gehäuse erlauben dabei durch die flächige Anordnung der Balls extrem hohe Anschlusszahlen<br />

bei eher moderaten Anschlussdichten: Der Ball Pitch von BGAs liegt bei 1,27mm, bei<br />

Micro-BGAs derzeit zwischen 0,65mm und 1,0mm, wobei allerdings noch Steigerungen der<br />

Dichte möglich sind. BGAs <strong>mit</strong> über 2000 Anschlüssen werden heute bereits eingesetzt.<br />

Darüber hinaus erlauben BGAs äußerst flexible<br />

Lösungen, die bei Plastikgehäusen <strong>mit</strong><br />

gestanztem Lead Frame kaum möglich sind.<br />

Insbesondere Mehrchip-Module lassen sich<br />

als PBGAs fast ohne zusätzliche technologische<br />

Anforderungen realisieren. So erforderte<br />

die in Abschnitt 3.1.2 auf Seite 19 geschilderte<br />

technologische Unvereinbarkeit einer DRAMund<br />

Flash-Integration in einem konzipierten<br />

ASIC-Projekt den gemeinsamen Aufbau eines<br />

Abbildung 5-12: Aluminium-BGA-Gehäuse <strong>mit</strong> 600<br />

Anschlüssen (Originalgröße 45×45mm), hier <strong>mit</strong><br />

einem Testchip für Zuverlässigkeitsuntersuchungen<br />

Lötseite<br />

Abbildung 5-13: Studie eines 2-Chip-BGA-Gehäuses<br />

(1 ASIC und 1 SDRAM, Originalgröße 19×11mm)<br />

ASICs <strong>mit</strong> internem Flash und eines SDRAMs in einem möglichst kleinen Gehäuse. Eine geeignete<br />

Lösung als 2-Chip-PBGA, bei der beide Dies in Chip-on-Board-Technik auf ein FR4-Substrat<br />

gebondet werden, zeigt Abbildung 5-13.<br />

ASIC<br />

SDRAM