pdf-Datei mit 72-dpi-Fotos - FG Mikroelektronik, TU Berlin

pdf-Datei mit 72-dpi-Fotos - FG Mikroelektronik, TU Berlin

pdf-Datei mit 72-dpi-Fotos - FG Mikroelektronik, TU Berlin

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

Dissertation<br />

Perspektiven des modernen ASIC-Designs<br />

Kapitel 5.1<br />

Seite 80<br />

den Zusammenhang von Teilen des Programmspeichers bei einem Spannungsausfall verloren<br />

gehen. Diesen Kopiervorgang kann die CPU ebenso wie die Berechnungen der Tabellen selbst<br />

ausführen.<br />

Das bis hierher vorgestellte Konzept ist bereits gut auf den Flash-Programmspeicher in einem<br />

SoC anwendbar. In dem SoC, für welches das Konzept entwickelt wurde, gab es allerdings noch<br />

zusätzliche Performance-Anforderungen an den Flash-Datenspeicher. Dieser sollte zum Teil als<br />

„Silicon Disk“ eingesetzt werden. Da die Programmierung eines Flashs äußerst langsam erfolgt –<br />

die Schreibzeit pro Wort lag bei 40μs, die Lesezugriffszeit bei 40ns – sollte aus Performancegründen<br />

ein Cache-System zum Beschreiben des Flashs konstruiert werden. Außerdem musste<br />

das Problem von zur Laufzeit entstehenden Defekten berücksichtigt werden, da einige Bereiche,<br />

insbesondere die FAT (file allocation table), sehr oft beschrieben werden sollten.<br />

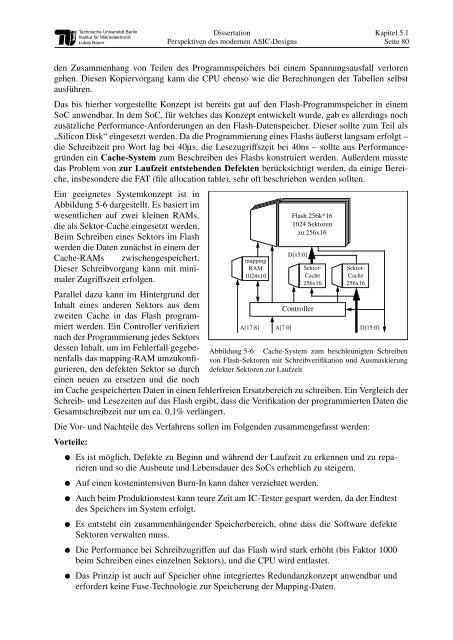

Ein geeignetes Systemkonzept ist in<br />

Abbildung 5-6 dargestellt. Es basiert im<br />

wesentlichen auf zwei kleinen RAMs,<br />

die als Sektor-Cache eingesetzt werden.<br />

Beim Schreiben eines Sektors im Flash<br />

werden die Daten zunächst in einem der<br />

Cache-RAMs zwischengespeichert.<br />

Dieser Schreibvorgang kann <strong>mit</strong> minimaler<br />

Zugriffszeit erfolgen.<br />

Parallel dazu kann im Hintergrund der<br />

Inhalt eines anderen Sektors aus dem<br />

zweiten Cache in das Flash programmiert<br />

werden. Ein Controller verifiziert<br />

nach der Programmierung jedes Sektors<br />

dessen Inhalt, um im Fehlerfall gegebenenfalls<br />

das mapping-RAM umzukonfigurieren,<br />

den defekten Sektor so durch<br />

einen neuen zu ersetzen und die noch<br />

im Cache gespeicherten Daten in einen fehlerfreien Ersatzbereich zu schreiben. Ein Vergleich der<br />

Schreib- und Lesezeiten auf das Flash ergibt, dass die Verifikation der programmierten Daten die<br />

Gesamtschreibzeit nur um ca. 0,1% verlängert.<br />

Die Vor- und Nachteile des Verfahrens sollen im Folgenden zusammengefasst werden:<br />

Vorteile:<br />

mapping<br />

RAM<br />

1024x10<br />

A[17:8]<br />

Flash 256k*16<br />

1024 Sektoren<br />

zu 256x16<br />

D[15:0]<br />

Abbildung 5-6: Cache-System zum beschleunigten Schreiben<br />

von Flash-Sektoren <strong>mit</strong> Schreibverifikation und Ausmaskierung<br />

defekter Sektoren zur Laufzeit<br />

● Es ist möglich, Defekte zu Beginn und während der Laufzeit zu erkennen und zu reparieren<br />

und so die Ausbeute und Lebensdauer des SoCs erheblich zu steigern.<br />

● Auf einen kostenintensiven Burn-In kann daher verzichtet werden.<br />

● Auch beim Produktionstest kann teure Zeit am IC-Tester gespart werden, da der Endtest<br />

des Speichers im System erfolgt.<br />

● Es entsteht ein zusammenhängender Speicherbereich, ohne dass die Software defekte<br />

Sektoren verwalten muss.<br />

● Die Performance bei Schreibzugriffen auf das Flash wird stark erhöht (bis Faktor 1000<br />

beim Schreiben eines einzelnen Sektors), und die CPU wird entlastet.<br />

● Das Prinzip ist auch auf Speicher ohne integriertes Redundanzkonzept anwendbar und<br />

erfordert keine Fuse-Technologie zur Speicherung der Mapping-Daten.<br />

A[7:0]<br />

Sektor-<br />

Cache<br />

256x16<br />

Controller<br />

Sektor-<br />

Cache<br />

256x16<br />

D[15:0]