pdf-Datei mit 72-dpi-Fotos - FG Mikroelektronik, TU Berlin

pdf-Datei mit 72-dpi-Fotos - FG Mikroelektronik, TU Berlin

pdf-Datei mit 72-dpi-Fotos - FG Mikroelektronik, TU Berlin

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

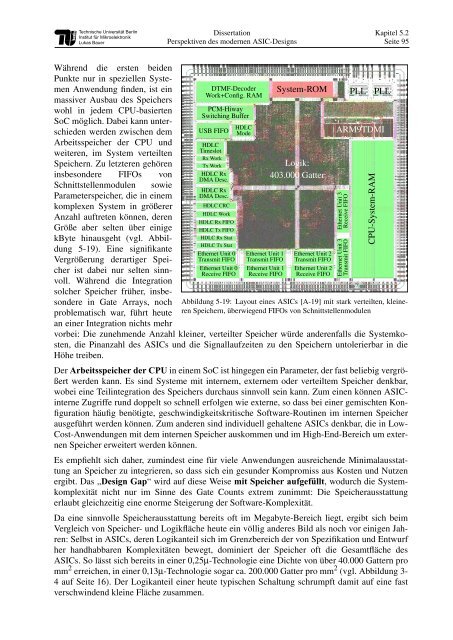

Während die ersten beiden<br />

Punkte nur in speziellen Systemen<br />

Anwendung finden, ist ein<br />

massiver Ausbau des Speichers<br />

wohl in jedem CPU-basierten<br />

SoC möglich. Dabei kann unterschieden<br />

werden zwischen dem<br />

Arbeitsspeicher der CPU und<br />

weiteren, im System verteilten<br />

Speichern. Zu letzteren gehören<br />

insbesondere FIFOs von<br />

Schnittstellenmodulen sowie<br />

Parameterspeicher, die in einem<br />

komplexen System in größerer<br />

Anzahl auftreten können, deren<br />

Größe aber selten über einige<br />

kByte hinausgeht (vgl. Abbildung<br />

5-19). Eine signifikante<br />

Vergrößerung derartiger Speicher<br />

ist dabei nur selten sinnvoll.<br />

Während die Integration<br />

solcher Speicher früher, insbesondere<br />

in Gate Arrays, noch<br />

problematisch war, führt heute<br />

an einer Integration nichts mehr<br />

Dissertation<br />

Perspektiven des modernen ASIC-Designs<br />

DTMF-Decoder<br />

Work+Config. RAM<br />

PCM-Hiway<br />

Switching Buffer<br />

USB FIFO HDLC<br />

Mode<br />

HDLC<br />

Timeslot<br />

Rx Work<br />

Tx Work<br />

HDLC Rx<br />

DMA Desc.<br />

HDLC Rx<br />

DMA Desc.<br />

HDLC CRC<br />

HDLC Work<br />

HDLC Rx FIFO<br />

HDLC Tx FIFO<br />

HDLC Rx Stat<br />

HDLC Tx Stat<br />

Ethernet Unit 0<br />

Trans<strong>mit</strong> FIFO<br />

Ethernet Unit 0<br />

Receive FIFO<br />

Ethernet Unit 1<br />

Trans<strong>mit</strong> FIFO<br />

Ethernet Unit 1<br />

Receive FIFO<br />

System-ROM<br />

Logik:<br />

403.000 Gatter<br />

Ethernet Unit 2<br />

Trans<strong>mit</strong> FIFO<br />

Ethernet Unit 2<br />

Receive FIFO<br />

PLL PLL<br />

Trans<strong>mit</strong> FIFO<br />

CPU-System-RAM<br />

ARM9TDMI<br />

Kapitel 5.2<br />

Seite 95<br />

Abbildung 5-19: Layout eines ASICs [A-19] <strong>mit</strong> stark verteilten, kleineren<br />

Speichern, überwiegend FIFOs von Schnittstellenmodulen<br />

vorbei: Die zunehmende Anzahl kleiner, verteilter Speicher würde anderenfalls die Systemkosten,<br />

die Pinanzahl des ASICs und die Signallaufzeiten zu den Speichern untolerierbar in die<br />

Höhe treiben.<br />

Der Arbeitsspeicher der CPU in einem SoC ist hingegen ein Parameter, der fast beliebig vergrößert<br />

werden kann. Es sind Systeme <strong>mit</strong> internem, externem oder verteiltem Speicher denkbar,<br />

wobei eine Teilintegration des Speichers durchaus sinnvoll sein kann. Zum einen können ASICinterne<br />

Zugriffe rund doppelt so schnell erfolgen wie externe, so dass bei einer gemischten Konfiguration<br />

häufig benötigte, geschwindigkeitskritische Software-Routinen im internen Speicher<br />

ausgeführt werden können. Zum anderen sind individuell gehaltene ASICs denkbar, die in Low-<br />

Cost-Anwendungen <strong>mit</strong> dem internen Speicher auskommen und im High-End-Bereich um externen<br />

Speicher erweitert werden können.<br />

Es empfiehlt sich daher, zumindest eine für viele Anwendungen ausreichende Minimalausstattung<br />

an Speicher zu integrieren, so dass sich ein gesunder Kompromiss aus Kosten und Nutzen<br />

ergibt. Das „Design Gap“ wird auf diese Weise <strong>mit</strong> Speicher aufgefüllt, wodurch die Systemkomplexität<br />

nicht nur im Sinne des Gate Counts extrem zunimmt: Die Speicherausstattung<br />

erlaubt gleichzeitig eine enorme Steigerung der Software-Komplexität.<br />

Da eine sinnvolle Speicherausstattung bereits oft im Megabyte-Bereich liegt, ergibt sich beim<br />

Vergleich von Speicher- und Logikfläche heute ein völlig anderes Bild als noch vor einigen Jahren:<br />

Selbst in ASICs, deren Logikanteil sich im Grenzbereich der von Spezifikation und Entwurf<br />

her handhabbaren Komplexitäten bewegt, dominiert der Speicher oft die Gesamtfläche des<br />

ASICs. So lässt sich bereits in einer 0,25μ-Technologie eine Dichte von über 40.000 Gattern pro<br />

mm 2 erreichen, in einer 0,13μ-Technologie sogar ca. 200.000 Gatter pro mm 2 (vgl. Abbildung 3-<br />

4 auf Seite 16). Der Logikanteil einer heute typischen Schaltung schrumpft da<strong>mit</strong> auf eine fast<br />

verschwindend kleine Fläche zusammen.<br />

Ethernet Unit 3<br />

Receive FIFO<br />

Ethernet Unit 3