- Page 2 and 3:

Volumes II I Index and Cross Refere

- Page 4 and 5:

M01'OROLA LINEAR/INTERFACE ICs DEVI

- Page 6:

Index and Cross Reference In Brief

- Page 23 and 24:

MOTOROLA LlNEARIiNTERFACE ICs DEVIC

- Page 25 and 26:

Precision Low Voltage References A

- Page 27:

MOTOROLA - SEMICONDUCTOR ----- TE

- Page 35 and 36:

MOTOROLA - SEMICONDUCTOR ----- TE

- Page 47 and 48:

Vin = 10VIo2OV + 22oo"F TL431 , A,

- Page 49 and 50:

Data Conversion The line of data co

- Page 51 and 52:

Data Conversion Package Overview MO

- Page 54:

MAXIMUM RATINGS (TA = 25'C unless o

- Page 62 and 63:

MOTOROLA - SEMICONDUCTOR ----__ TEC

- Page 66 and 67:

The MC1408 consists of a reference

- Page 70:

Voltage outputs of a larger magnitu

- Page 75 and 76:

ABSOLUTE MAXIMUM RATINGS MC10319 Pa

- Page 77:

MC10319 TIMING CHARACTERISTICS (TA

- Page 82 and 83:

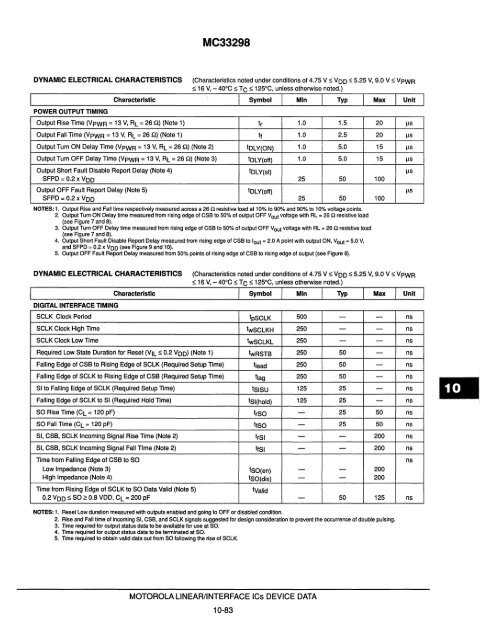

ICC(A) is nominally 17 mA, and does

- Page 84 and 85:

VIDEO APPUCATIONS The MC10319 is su

- Page 91 and 92:

APERTURE DELAY - The time differenc

- Page 94 and 95:

MC10321 ELECTRICAL CHARACTERISTICS

- Page 99 and 100:

applied to the reference must be su

- Page 101 and 102:

VIDEO APPLICATIONS The MC10321 is s

- Page 107:

Vin 0-25 MHz Clock +2.0 V 500 n (Op

- Page 111:

Symbol Pin 00-07 1-4, 21-24 DGnd 5

- Page 124:

Glitch Area - The energy content of

- Page 127 and 128:

MAXIMUM RATINGS MC10324 Characteris

- Page 136:

Digitally Modulating an Analog Sign

- Page 140:

Interface Circuits In Brief ... Des

- Page 149:

Interface Circuits Device AM26LS30

- Page 158:

Operating Temperature Range The max

- Page 161:

MOTOROLA - SEMICONDUCTOR ----- TE

- Page 165:

AM26LS32 MAXIMUM RATINGS Rating Sym

- Page 172 and 173:

MOTOROLA SEMICONDUCTOR----- TECHN

- Page 180 and 181:

MOTOROLA - SEMICONDUCTOR ----__ TEC

- Page 194:

MOTOROLA SEMICONDUCTOR----- TECHN

- Page 200:

MOTOROLA SEMICONDUCTOR----- TECHN

- Page 209:

MC3437 ELECTRICAL CHARACTERISTICS (

- Page 215:

------..., I 2 MC3447s i I I OAV 01

- Page 233:

MOTOROLA - SEMICONDUCTOR ----- TE

- Page 239 and 240:

MAXIMUM RATINGS (TA = 25°C) MC3469

- Page 242:

MC3469 AC SWITCHING CHARACTERISTICS

- Page 249:

MAXIMUM RATINGS (TA=25°C) MC3470,

- Page 262 and 263:

MOTOROLA - SEMICONDUCTOR ----- TE

- Page 266:

MC3471 AC SWITCHING CHARACTERISTICS

- Page 278 and 279:

MOTOROLA - SEMICONDUCTOR - ____ _ T

- Page 282:

MAXIMUM RATINGS MC3487 Roting Symbo

- Page 291:

OPERATING DYNAMIC POWER SUPPLY CURR

- Page 301 and 302:

MAXIMUM RATINGS MC34050, MC34051 Pa

- Page 306:

MC34050, MC34051 FIGURE 16 - EIA·4

- Page 318:

MC75S110 ELECTRICAL CHARACTERISTICS

- Page 323 and 324:

MC751728, MC751748 ELECTRICAL CHARA

- Page 329 and 330:

used) and at what current levels th

- Page 331:

MC75172B, MC75174B Comparing System

- Page 342 and 343:

ULN2801, ULN2802, ULN2803, ULN2804

- Page 346:

Communication Circuits In Brief ...

- Page 352 and 353:

Subscriber Loop Interface Circuits

- Page 354:

PCM Mono-Circuits Codec-Filters MC1

- Page 357:

ISDN Voice/Data Circuits Integrated

- Page 360:

Voice/Data Communication (Digital T

- Page 368 and 369:

Telephone Accessory Circuits (conti

- Page 372:

Summary of Bipolar Telecom Circuits

- Page 375 and 376:

RF Communications Device MC1496, MC

- Page 388:

MAXIMUM RATINGS MC2830 Rating Symbo

- Page 395:

MAXIMUM RATINGS MC2833 Ratings Symb

- Page 398:

MC2833 FIGURE 9 - 144 MHzlX12 MULTI

- Page 403:

CIRCUIT DESCRIPTION The MC3335 is a

- Page 412:

CIRCUIT DESCRIPTION The MC3357 is a

- Page 421:

MAXIMUM RATINGS (TA = 25°C unless

- Page 426:

VCC = 4.0 V 1st IF 10.7 MHz from In

- Page 434:

MOTOROLA - SEMICONDUCTOR ----- TE

- Page 450 and 451:

Data Buffer Design The data buffer

- Page 454:

VCC = 4.0 Vdc Cl o.ot MC3371, MC337

- Page 469:

MAXIMUM RATINGS MC13055 Rating Symb

- Page 474:

The MC13055 is an extended frequenc

- Page 477:

MAXIMUM RATINGS MC13135, MC13136 Ra

- Page 494 and 495:

S-Parameters (VEE =-5.0 Vdc, TA = 2

- Page 496:

MC13155 S-Parameters (VEE = - 3.0 V

- Page 503 and 504:

MOTOROLA SEMICONDUCTOR ____ _ TECHN

- Page 508:

Pin Symbol 9 Xtalb 10 Reg. Gnd 11 E

- Page 520 and 521:

MC13175, MC13176 Figure 26. Circuit

- Page 522 and 523:

MOTOROLA SEMICONDUCTOR---- TECHNI

- Page 524 and 525:

Addendum An Introduction to Motorol

- Page 526 and 527:

COMMUNICATIONS SYSTEMS For the most

- Page 528 and 529:

In addition, there are many PC and

- Page 530 and 531:

Consumer Electronic Circuits In Bri

- Page 532 and 533:

Video Circuits Video Circuits Encod

- Page 535:

Video Circuits (continued) Bringing

- Page 540 and 541:

Video Circuits (continued) TV Stere

- Page 542:

Video Circuits (continued) Subcarri

- Page 545 and 546:

Video Circuits (continued) Multista

- Page 548 and 549:

Video Circuits (continued) PLL Tuni

- Page 550:

Video Circuits (continued) Advanced

- Page 556 and 557:

MOTOROLA SEMICONDUCTOR----- TECHN

- Page 558:

CA3146 ELECTRICAL CHARACTERICISTICS

- Page 570:

MAXIMUM RATINGS (TA = +25°C, unles

- Page 581:

AM Section The AM modulator transfe

- Page 588:

MC1377 ELECTRICAL CHARACTERICISTICS

- Page 603:

MAXIMUM RATINGS MC1378 Rating Symbo

- Page 609:

MC1388 ELECTRICAL CHARACTERISTICS (

- Page 622:

+2.0 V + Sine V Pin 28 -2.0 V +2.0V

- Page 629:

MOTOROLA SEMICONDUCTOR----- TECHN

- Page 635:

MOTOROLA SEMICONDUCTOR----- TECHN

- Page 653:

In the PLL filter circuit on Pin 19

- Page 660:

MAXIMUM RATINGS MC13024 Rating Symb

- Page 671:

MAXIMUM RAnNGS MC13077 Rating Symbo

- Page 692 and 693:

Figure 1 shows a simplified block d

- Page 694:

12C Bus It is not within the scope

- Page 697:

In addition, components are added t

- Page 700:

up/down counter and decoder.The cou

- Page 704:

B-Y and R-Y Inputs (Pin 26, 27) - C

- Page 707 and 708:

MC44001 Table 2. Control Bit Truth

- Page 709 and 710:

When the Address Read/Write bit is

- Page 714 and 715:

MAXIMUM RATINGS MC44011 Parameter S

- Page 716:

MC44011 ELECTRICAL CHARACTERISTICS

- Page 734:

Introduction The MC44011, a member

- Page 741 and 742:

The Field ID output (Pin 7) indicat

- Page 743:

Control Bit Name $77-7 S·VHS·V $7

- Page 747:

PinNa. Name 1, Video 1, 3 Video 2 2

- Page 755:

Enable Horizontal lime base Set $86

- Page 761:

+5.0 Voltage Reference 2.6V Subcarr

- Page 770:

IF Amplifier and AGe The IF amplifi

- Page 774 and 775:

clamp is released, the veo offset i

- Page 776:

24 Pin 28 Pin (DIP) (SOIC) 1,21, 1,

- Page 782 and 783:

HI 0 Figure 15. Component Placement

- Page 784 and 785:

MOTOROLA SEMICONDUCTOR----- TECHN

- Page 787:

MOTOROLA SEMICONDUCTOR----- TECHN

- Page 795 and 796:

Optional Waveform Disable Pin 2 on

- Page 801:

+HV Pin 19 -HV Pin 20 +Hv2 Pin 28 -

- Page 809 and 810:

DATA FORMAT AND BUS RECEIVER The ci

- Page 812:

Pin (Max 2.8m V pp) 50Hz VTuning MC

- Page 816:

T3 a 1 MC44807/17 DEFINITION OF THE

- Page 823 and 824:

The control and band information bi

- Page 825 and 826:

D/A Converters - The D/A converters

- Page 827:

MAXIMUM RATINGS TDA3190 Rating Symb

- Page 830:

MAXIMUM RATINGS (TA = + 25°C, unle

- Page 836 and 837:

ACC and Identification Detectors Du

- Page 841:

TDA33018 Figure 18. Typical Video O

- Page 844:

Automotive Electronic Circuits In B

- Page 848 and 849:

High Side TMOS Driver MC33091 P, 0

- Page 850 and 851:

Voltage Regulators Device LM2931 Se

- Page 852:

MC3325 ELECTRICAL CHARACTERICISTICS

- Page 859:

MAXIMUM RATINGS MC3391 Rating Symbo

- Page 868:

MAXIMUM RATINGS MC3392 Rating Symbo

- Page 878: 800 V o o ,.. 40V- Ignition 12V- In

- Page 895 and 896: 10. Calculate the shorted load aver

- Page 897 and 898: MOTOROLA SEMICONDUCTOR----- TECHN

- Page 902 and 903: MC33092 PIN FUNCTION DESCRIPTION Pi

- Page 904 and 905: The digital ON-time is determined b

- Page 912 and 913: Darlington Drive The Darlington Dri

- Page 915: Test and Reliability Both visual in

- Page 923: MC33298 MAXIMUM RATINGS (All voltag

- Page 939 and 940: MC33298 Table 1. Program to Exercis

- Page 946: The use of Cin is not mandatory, an

- Page 950 and 951: Other Linear Circuits In Brief ...

- Page 952 and 953: Smoke Detectors (CMOS) These smoke

- Page 955: II MAXIMUM RATINGS (TA = +25°C, un

- Page 974:

TOTAL DC ACCURACY - The total DC ac

- Page 998:

Surface Mount Technology In Brief .

- Page 1001:

MC13024DW MC13055D MC13060D MC33023

- Page 1004 and 1005:

Remote Control Functions MC14469FN

- Page 1006 and 1007:

Analog MPQ Table Tape/Reel and Ammo

- Page 1009 and 1010:

MOTOROLA LINEAR/INTERFACE ICs DEVIC

- Page 1028 and 1029:

Quality and Reliability Assurance I

- Page 1031:

Figure 4. Portion of a Process Flow

- Page 1036 and 1037:

humidity independently of each othe

- Page 1038 and 1039:

Applications and Product Literature

- Page 1040 and 1041:

Applications and Product Literature

- Page 1042 and 1043:

Applications and Product Literature

- Page 1044 and 1045:

Applications and Product literature