Avalon Interface Specifications (PDF) - Altera

Avalon Interface Specifications (PDF) - Altera

Avalon Interface Specifications (PDF) - Altera

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapter 2: <strong>Avalon</strong> Clock and Reset <strong>Interface</strong>s 2–3<br />

Reset <strong>Interface</strong>s<br />

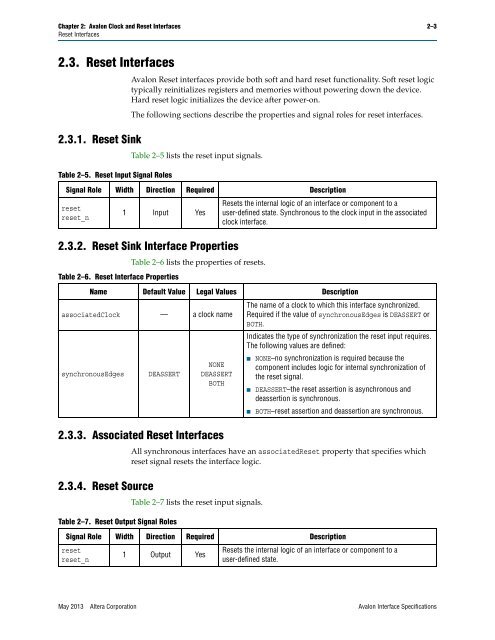

2.3. Reset <strong>Interface</strong>s<br />

2.3.1. Reset Sink<br />

Table 2–5. Reset Input Signal Roles<br />

<strong>Avalon</strong> Reset interfaces provide both soft and hard reset functionality. Soft reset logic<br />

typically reinitializes registers and memories without powering down the device.<br />

Hard reset logic initializes the device after power-on.<br />

The following sections describe the properties and signal roles for reset interfaces.<br />

Table 2–5 lists the reset input signals.<br />

Signal Role Width Direction Required Description<br />

reset<br />

reset_n<br />

2.3.2. Reset Sink <strong>Interface</strong> Properties<br />

Table 2–6 lists the properties of resets.<br />

2.3.3. Associated Reset <strong>Interface</strong>s<br />

2.3.4. Reset Source<br />

1 Input Yes<br />

Table 2–6. Reset <strong>Interface</strong> Properties<br />

All synchronous interfaces have an associatedReset property that specifies which<br />

reset signal resets the interface logic.<br />

Table 2–7 lists the reset input signals.<br />

Resets the internal logic of an interface or component to a<br />

user-defined state. Synchronous to the clock input in the associated<br />

clock interface.<br />

Name Default Value Legal Values Description<br />

associatedClock — a clock name<br />

synchronousEdges DEASSERT<br />

Table 2–7. Reset Output Signal Roles<br />

NONE<br />

DEASSERT<br />

BOTH<br />

The name of a clock to which this interface synchronized.<br />

Required if the value of synchronousEdges is DEASSERT or<br />

BOTH.<br />

Indicates the type of synchronization the reset input requires.<br />

The following values are defined:<br />

■ NONE–no synchronization is required because the<br />

component includes logic for internal synchronization of<br />

the reset signal.<br />

■ DEASSERT–the reset assertion is asynchronous and<br />

deassertion is synchronous.<br />

■ BOTH–reset assertion and deassertion are synchronous.<br />

Signal Role Width Direction Required Description<br />

reset<br />

reset_n<br />

1 Output Yes<br />

Resets the internal logic of an interface or component to a<br />

user-defined state.<br />

May 2013 <strong>Altera</strong> Corporation <strong>Avalon</strong> <strong>Interface</strong> <strong>Specifications</strong>