Avalon Interface Specifications (PDF) - Altera

Avalon Interface Specifications (PDF) - Altera

Avalon Interface Specifications (PDF) - Altera

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

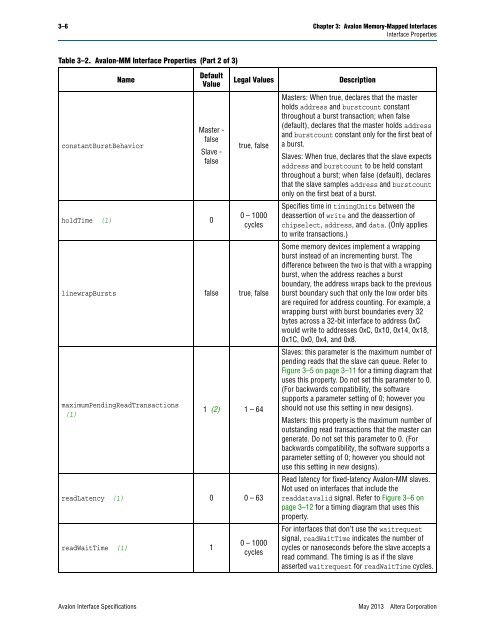

3–6 Chapter 3: <strong>Avalon</strong> Memory-Mapped <strong>Interface</strong>s<br />

<strong>Interface</strong> Properties<br />

Table 3–2. <strong>Avalon</strong>-MM <strong>Interface</strong> Properties (Part 2 of 3)<br />

Name<br />

constantBurstBehavior<br />

Master -<br />

false<br />

Slave -<br />

false<br />

holdTime (1) 0<br />

true, false<br />

0 – 1000<br />

cycles<br />

linewrapBursts false true, false<br />

maximumPendingReadTransactions<br />

(1)<br />

Default<br />

Value<br />

1 (2) 1 – 64<br />

readLatency (1) 0 0 – 63<br />

readWaitTime (1) 1<br />

Legal Values Description<br />

0 – 1000<br />

cycles<br />

Masters: When true, declares that the master<br />

holds address and burstcount constant<br />

throughout a burst transaction; when false<br />

(default), declares that the master holds address<br />

and burstcount constant only for the first beat of<br />

a burst.<br />

Slaves: When true, declares that the slave expects<br />

address and burstcount to be held constant<br />

throughout a burst; when false (default), declares<br />

that the slave samples address and burstcount<br />

only on the first beat of a burst.<br />

Specifies time in timingUnits between the<br />

deassertion of write and the deassertion of<br />

chipselect, address, and data. (Only applies<br />

to write transactions.)<br />

Some memory devices implement a wrapping<br />

burst instead of an incrementing burst. The<br />

difference between the two is that with a wrapping<br />

burst, when the address reaches a burst<br />

boundary, the address wraps back to the previous<br />

burst boundary such that only the low order bits<br />

are required for address counting. For example, a<br />

wrapping burst with burst boundaries every 32<br />

bytes across a 32-bit interface to address 0xC<br />

would write to addresses 0xC, 0x10, 0x14, 0x18,<br />

0x1C, 0x0, 0x4, and 0x8.<br />

Slaves: this parameter is the maximum number of<br />

pending reads that the slave can queue. Refer to<br />

Figure 3–5 on page 3–11 for a timing diagram that<br />

uses this property. Do not set this parameter to 0.<br />

(For backwards compatibility, the software<br />

supports a parameter setting of 0; however you<br />

should not use this setting in new designs).<br />

Masters: this property is the maximum number of<br />

outstanding read transactions that the master can<br />

generate. Do not set this parameter to 0. (For<br />

backwards compatibility, the software supports a<br />

parameter setting of 0; however you should not<br />

use this setting in new designs).<br />

Read latency for fixed-latency <strong>Avalon</strong>-MM slaves.<br />

Not used on interfaces that include the<br />

readdatavalid signal. Refer to Figure 3–6 on<br />

page 3–12 for a timing diagram that uses this<br />

property.<br />

For interfaces that don’t use the waitrequest<br />

signal, readWaitTime indicates the number of<br />

cycles or nanoseconds before the slave accepts a<br />

read command. The timing is as if the slave<br />

asserted waitrequest for readWaitTime cycles.<br />

<strong>Avalon</strong> <strong>Interface</strong> <strong>Specifications</strong> May 2013 <strong>Altera</strong> Corporation