Avalon Interface Specifications (PDF) - Altera

Avalon Interface Specifications (PDF) - Altera

Avalon Interface Specifications (PDF) - Altera

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Chapter 5: <strong>Avalon</strong> Streaming <strong>Interface</strong>s 5–9<br />

Packet Data Transfers<br />

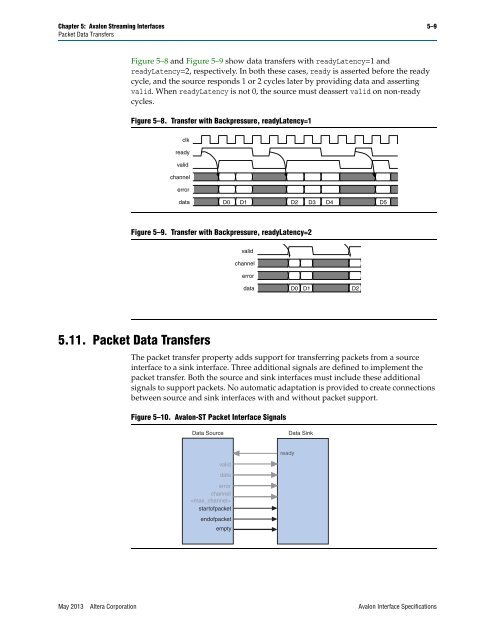

Figure 5–8 and Figure 5–9 show data transfers with readyLatency=1 and<br />

readyLatency=2, respectively. In both these cases, ready is asserted before the ready<br />

cycle, and the source responds 1 or 2 cycles later by providing data and asserting<br />

valid. When readyLatency is not 0, the source must deassert valid on non-ready<br />

cycles.<br />

Figure 5–8. Transfer with Backpressure, readyLatency=1<br />

Figure 5–9. Transfer with Backpressure, readyLatency=2<br />

5.11. Packet Data Transfers<br />

clk<br />

ready<br />

valid<br />

channel<br />

error<br />

data D0 D1 D2 D3 D4 D5<br />

valid<br />

channel<br />

error<br />

data D0 D1 D2<br />

The packet transfer property adds support for transferring packets from a source<br />

interface to a sink interface. Three additional signals are defined to implement the<br />

packet transfer. Both the source and sink interfaces must include these additional<br />

signals to support packets. No automatic adaptation is provided to create connections<br />

between source and sink interfaces with and without packet support.<br />

Figure 5–10. <strong>Avalon</strong>-ST Packet <strong>Interface</strong> Signals<br />

Data Source Data Sink<br />

valid<br />

data<br />

error<br />

channel<br />

<br />

startofpacket<br />

endofpacket<br />

empty<br />

May 2013 <strong>Altera</strong> Corporation <strong>Avalon</strong> <strong>Interface</strong> <strong>Specifications</strong><br />

ready