Avalon Interface Specifications (PDF) - Altera

Avalon Interface Specifications (PDF) - Altera

Avalon Interface Specifications (PDF) - Altera

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

5–10 Chapter 5: <strong>Avalon</strong> Streaming <strong>Interface</strong>s<br />

Signal Details<br />

5.12. Signal Details<br />

5.13. Protocol Details<br />

The following paragraphs provide more details about these three signals:<br />

■ startofpacket—The startofpacket signal is required by all interfaces supporting<br />

packet transfers and marks the active cycle containing the start of the packet. This<br />

signal is only interpreted when valid is asserted.<br />

■ endofpacket—The endofpacket signal is required by all interfaces supporting<br />

packet transfer and marks the active cycle containing the end of the packet. This<br />

signal is only interpreted when valid is asserted. startofpacket and endofpacket<br />

can be asserted in the same cycle. No idle cycles are required between packets, so<br />

that the startofpacket signal can follow immediately after the previous<br />

endofpacket signal.<br />

■ empty—The optional empty signal indicates the number of symbols that are empty<br />

during the cycles that mark the end of a packet. The sink only checks the value of<br />

the empty during active cycles that have endofpacket asserted. The empty symbols<br />

are always the last symbols in data, those carried by the low-order bits when<br />

firstSymbolInHighOrderBits = true. The empty signal is required on all packet<br />

interfaces whose data signal carries more than one symbol of data and have a<br />

variable length packet format. The size of the empty signal in bits is log 2().<br />

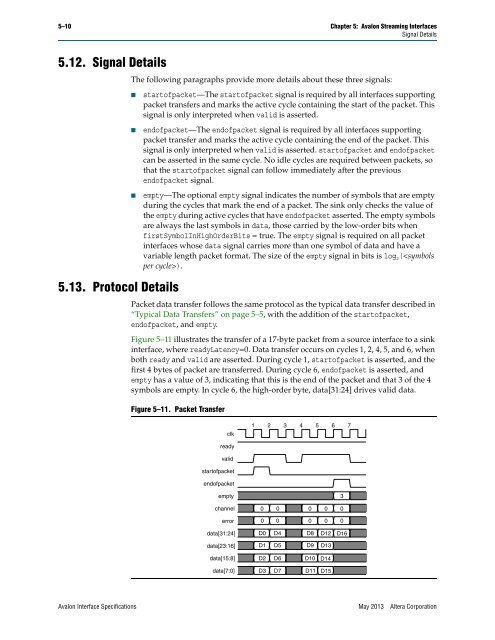

Packet data transfer follows the same protocol as the typical data transfer described in<br />

“Typical Data Transfers” on page 5–5, with the addition of the startofpacket,<br />

endofpacket, and empty.<br />

Figure 5–11 illustrates the transfer of a 17-byte packet from a source interface to a sink<br />

interface, where readyLatency=0. Data transfer occurs on cycles 1, 2, 4, 5, and 6, when<br />

both ready and valid are asserted. During cycle 1, startofpacket is asserted, and the<br />

first 4 bytes of packet are transferred. During cycle 6, endofpacket is asserted, and<br />

empty has a value of 3, indicating that this is the end of the packet and that 3 of the 4<br />

symbols are empty. In cycle 6, the high-order byte, data[31:24] drives valid data.<br />

Figure 5–11. Packet Transfer<br />

clk<br />

ready<br />

valid<br />

startofpacket<br />

endofpacket<br />

empty<br />

channel<br />

error<br />

data[31:24]<br />

data[23:16]<br />

data[15:8]<br />

data[7:0]<br />

1 2 3 4 5 6 7<br />

0 0 0 0 0<br />

0 0 0 0 0<br />

D0 D4 D8 D12 D16<br />

D1 D5 D9 D13<br />

D2 D6 D10 D14<br />

D3 D7 D11 D15<br />

<strong>Avalon</strong> <strong>Interface</strong> <strong>Specifications</strong> May 2013 <strong>Altera</strong> Corporation<br />

3