Avalon Interface Specifications (PDF) - Altera

Avalon Interface Specifications (PDF) - Altera

Avalon Interface Specifications (PDF) - Altera

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapter 5: <strong>Avalon</strong> Streaming <strong>Interface</strong>s 5–5<br />

Typical Data Transfers<br />

Table 5–2. <strong>Avalon</strong>-ST <strong>Interface</strong> Properties (Part 2 of 2)<br />

Property Name<br />

5.6. Typical Data Transfers<br />

5.7. Signal Details<br />

Default<br />

Value<br />

maxChannel 0 0 – 255<br />

readyLatency 0 0 – 8<br />

Legal Values Description<br />

The maximum number of channels that a data interface can<br />

support.<br />

Defines the relationship between assertion and deassertion of<br />

the ready signal, and cycles which are considered to be ready<br />

for data transfer, separately for each interface.<br />

This section defines the transfer of data from a source interface to a sink interface. In<br />

all cases, the data source and the data sink must comply with the specification. It is<br />

not the responsibility of the data sink to detect source protocol errors.<br />

This section describes the basic <strong>Avalon</strong>-ST protocol that all data transfers must follow.<br />

It also highlights the flexibility available in choosing <strong>Avalon</strong>-ST signals to meet the<br />

needs of a particular component and makes recommendations about the signals that<br />

should be used.<br />

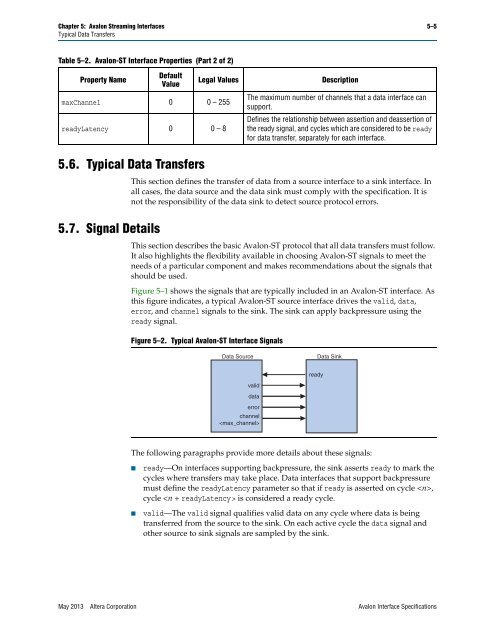

Figure 5–1 shows the signals that are typically included in an <strong>Avalon</strong>-ST interface. As<br />

this figure indicates, a typical <strong>Avalon</strong>-ST source interface drives the valid, data,<br />

error, and channel signals to the sink. The sink can apply backpressure using the<br />

ready signal.<br />

Figure 5–2. Typical <strong>Avalon</strong>-ST <strong>Interface</strong> Signals<br />

Data Source<br />

valid<br />

data<br />

error<br />

channel<br />

<br />

The following paragraphs provide more details about these signals:<br />

■ ready—On interfaces supporting backpressure, the sink asserts ready to mark the<br />

cycles where transfers may take place. Data interfaces that support backpressure<br />

must define the readyLatency parameter so that if ready is asserted on cycle ,<br />

cycle is considered a ready cycle.<br />

■ valid—The valid signal qualifies valid data on any cycle where data is being<br />

transferred from the source to the sink. On each active cycle the data signal and<br />

other source to sink signals are sampled by the sink.<br />

May 2013 <strong>Altera</strong> Corporation <strong>Avalon</strong> <strong>Interface</strong> <strong>Specifications</strong><br />

ready<br />

Data Sink