Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

5-14<br />

<strong>Controller</strong> <strong>External</strong> Interfaces<br />

emi_rm_004<br />

2013.12.16<br />

signal; the controller then deasserts the acknowledge signal when the memory device is no longer in selfrefresh<br />

mode.<br />

Note: For multi-rank designs using the <strong>HPC</strong> <strong>II</strong> memory controller, a self-refresh and a user-refresh cannot<br />

be made to the same memory chip simultaneously. Also, the self-refresh ack signal indicates that<br />

at least one device has entered self-refresh, but does not necessarily mean that all devices have entered<br />

self-refresh.<br />

User-Controlled Refresh Interface<br />

The optional user-controlled refresh interface consists of a request signal, a chip select signal, and an<br />

acknowledgement signal. This interface provides increased control over worst-case read latency and enables<br />

you to issue refresh bursts during idle periods. This interface is clocked by afi_clk.<br />

When you assert a refresh request signal to instruct the controller to perform a refresh operation, that request<br />

takes priority over any outstanding read or write requests that might be in the command queue. In addition<br />

to the request signal, you must also choose the chip to be refreshed by asserting the refresh chip select signal<br />

along with the request signal. If you do not assert the chip select signal with the request signal, unexpected<br />

behavior may result.<br />

The controller attempts to perform a refresh as long as the refresh request signal is asserted; if you require<br />

only one refresh, you should deassert the refresh request signal after the acknowledgement signal is received.<br />

If you maintain the request signal high after the acknowledgement is sent, it would indicate that further<br />

refresh is required. You should deassert the request signal after the required number of acknowledgement/refresh<br />

is received from the controller. You can issue up to a maximum of nine consecutive refresh<br />

commands.<br />

Note:<br />

For multi-rank designs using the <strong>HPC</strong> <strong>II</strong> memory controller, a self-refresh and a user-refresh cannot<br />

be made to the same memory chip simultaneously.<br />

Configuration and Status Register (CSR) Interface<br />

The controller has a configuration and status register (CSR) interface that allows you to configure timing<br />

parameters, address widths, and the behavior of the controller. The CSR interface is a 32-bit Avalon-MM<br />

slave of fixed address width; if you do not need this feature, you can disable it to save area.<br />

This interface is clocked by csr_clk, which is the same as afi_clk, and is always synchronous relative<br />

to the main data slave interface.<br />

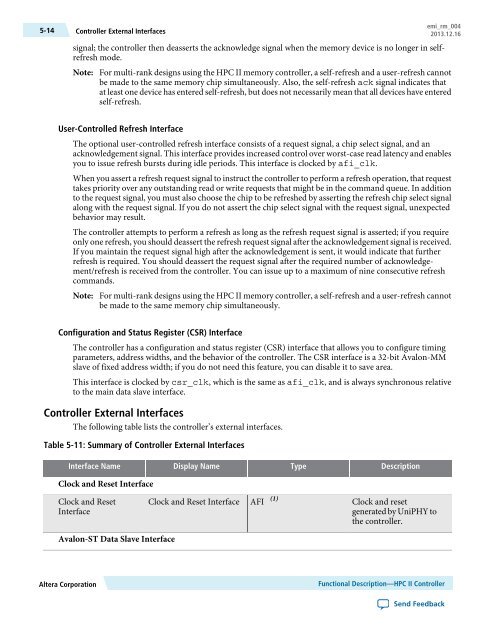

<strong>Controller</strong> <strong>External</strong> Interfaces<br />

The following table lists the controller’s external interfaces.<br />

Table 5-11: Summary of <strong>Controller</strong> <strong>External</strong> Interfaces<br />

Interface Name<br />

Display Name<br />

Type<br />

<strong>Description</strong><br />

Clock and Reset Interface<br />

Clock and Reset<br />

Interface<br />

Clock and Reset Interface<br />

AFI (1)<br />

Clock and reset<br />

generated by UniPHY to<br />

the controller.<br />

Avalon-ST Data Slave Interface<br />

<strong>Altera</strong> Corporation<br />

<strong>Functional</strong> <strong>Description</strong>—<strong>HPC</strong> <strong>II</strong> <strong>Controller</strong><br />

Send Feedback