Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

emi_rm_004<br />

2013.12.16<br />

Local Interface Signals<br />

5-21<br />

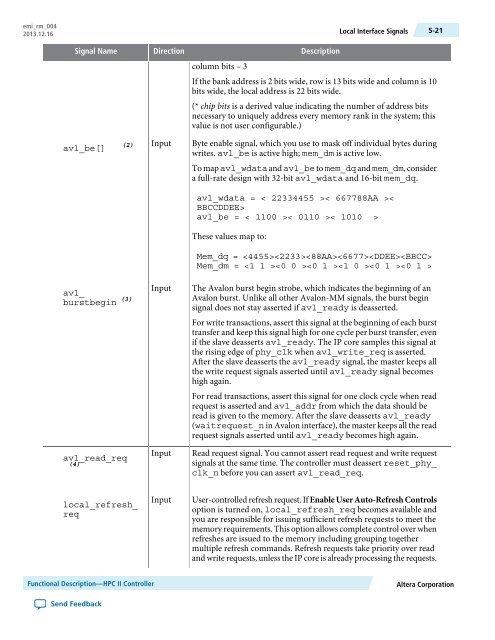

Signal Name<br />

Direction<br />

<strong>Description</strong><br />

column bits – 3<br />

If the bank address is 2 bits wide, row is 13 bits wide and column is 10<br />

bits wide, the local address is 22 bits wide.<br />

(* chip bits is a derived value indicating the number of address bits<br />

necessary to uniquely address every memory rank in the system; this<br />

value is not user configurable.)<br />

avl_be[]<br />

(2)<br />

Input<br />

Byte enable signal, which you use to mask off individual bytes during<br />

writes. avl_be is active high; mem_dm is active low.<br />

To map avl_wdata and avl_be to mem_dq and mem_dm, consider<br />

a full-rate design with 32-bit avl_wdata and 16-bit mem_dq.<br />

avl_wdata = < 22334455 >< 667788AA ><<br />

BBCCDDEE><br />

avl_be = < 1100 >< 0110 >< 1010 ><br />

These values map to:<br />

Mem_dq = <br />

Mem_dm = <br />

avl_<br />

burstbegin (3)<br />

avl_read_req<br />

(4)<br />

Input<br />

Input<br />

The Avalon burst begin strobe, which indicates the beginning of an<br />

Avalon burst. Unlike all other Avalon-MM signals, the burst begin<br />

signal does not stay asserted if avl_ready is deasserted.<br />

For write transactions, assert this signal at the beginning of each burst<br />

transfer and keep this signal high for one cycle per burst transfer, even<br />

if the slave deasserts avl_ready. The IP core samples this signal at<br />

the rising edge of phy_clk when avl_write_req is asserted.<br />

After the slave deasserts the avl_ready signal, the master keeps all<br />

the write request signals asserted until avl_ready signal becomes<br />

high again.<br />

For read transactions, assert this signal for one clock cycle when read<br />

request is asserted and avl_addr from which the data should be<br />

read is given to the memory. After the slave deasserts avl_ready<br />

(waitrequest_n in Avalon interface), the master keeps all the read<br />

request signals asserted until avl_ready becomes high again.<br />

Read request signal. You cannot assert read request and write request<br />

signals at the same time. The controller must deassert reset_phy_<br />

clk_n before you can assert avl_read_req.<br />

local_refresh_<br />

req<br />

Input<br />

User-controlled refresh request. If Enable User Auto-Refresh Controls<br />

option is turned on, local_refresh_req becomes available and<br />

you are responsible for issuing sufficient refresh requests to meet the<br />

memory requirements. This option allows complete control over when<br />

refreshes are issued to the memory including grouping together<br />

multiple refresh commands. Refresh requests take priority over read<br />

and write requests, unless the IP core is already processing the requests.<br />

<strong>Functional</strong> <strong>Description</strong>—<strong>HPC</strong> <strong>II</strong> <strong>Controller</strong><br />

<strong>Altera</strong> Corporation<br />

Send Feedback