Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

emi_rm_004<br />

2013.12.16<br />

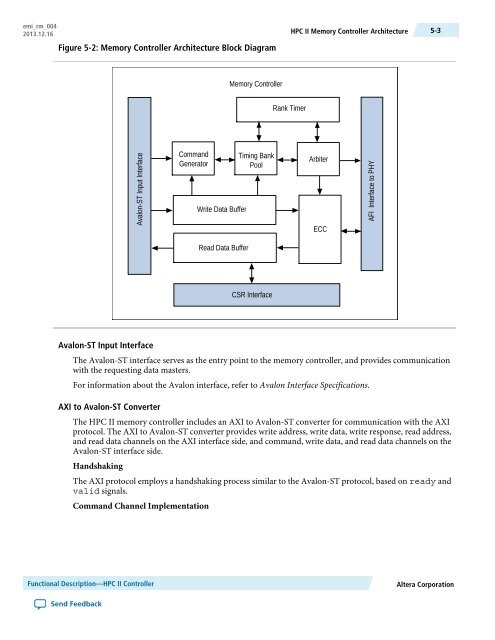

Figure 5-2: <strong>Memory</strong> <strong>Controller</strong> Architecture Block Diagram<br />

<strong>HPC</strong> <strong>II</strong> <strong>Memory</strong> <strong>Controller</strong> Architecture<br />

5-3<br />

<strong>Memory</strong> <strong>Controller</strong><br />

Rank Timer<br />

Avalon-ST Input Interface<br />

Command<br />

Generator<br />

Write Data Buffer<br />

Timing Bank<br />

Pool<br />

Arbiter<br />

ECC<br />

AFI Interface to PHY<br />

Read Data Buffer<br />

CSR Interface<br />

Avalon-ST Input Interface<br />

The Avalon-ST interface serves as the entry point to the memory controller, and provides communication<br />

with the requesting data masters.<br />

For information about the Avalon interface, refer to Avalon Interface Specifications.<br />

AXI to Avalon-ST Converter<br />

The <strong>HPC</strong> <strong>II</strong> memory controller includes an AXI to Avalon-ST converter for communication with the AXI<br />

protocol. The AXI to Avalon-ST converter provides write address, write data, write response, read address,<br />

and read data channels on the AXI interface side, and command, write data, and read data channels on the<br />

Avalon-ST interface side.<br />

Handshaking<br />

The AXI protocol employs a handshaking process similar to the Avalon-ST protocol, based on ready and<br />

valid signals.<br />

Command Channel Implementation<br />

<strong>Functional</strong> <strong>Description</strong>—<strong>HPC</strong> <strong>II</strong> <strong>Controller</strong><br />

<strong>Altera</strong> Corporation<br />

Send Feedback