Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

5-4<br />

Backpressure Support<br />

The AXI interface includes separate read and write channels, while the Avalon-ST interface has only one<br />

command channel. Arbitration of the read and write channels is based on these policies:<br />

• Round robin<br />

• Write priority—write channel has priority over read channel<br />

• Read priority—read channel has priority over write channel<br />

You can choose an arbitration policy by setting the COMMAND_ARB_TYPE parameter to one of<br />

ROUND_ROBIN, WRITE_PRIORITY, or READ_PRIORITY in the alt_mem_ddrx_axi_st_converter.v file.<br />

Data Ordering<br />

The AXI specification requires that write data IDs must arrive in the same order as write address IDs are<br />

received. Similarly, read data must be returned in the same order as its associated read address is received.<br />

Consequently, the AXI to Avalon-ST converter does not support interleaving of write data; all data must<br />

arrive in the same order as its associated write address IDs. On the read side, the controller returns read data<br />

based on the read addresses received.<br />

Burst Types<br />

The AXI to Avalon-ST converter supports the following burst types:<br />

emi_rm_004<br />

2013.12.16<br />

• Incrementing burst—the address for each transfer is an increment of the previous transfer address; the<br />

increment value depends on the size of the transfer.<br />

• Wrapping burst—similar to the incrementing burst, but wraps to the lower address when the burst<br />

boundary is reached. The starting address must be aligned to the size of the transfer. Burst length must<br />

be 2, 4, 8, or 16. The burst wrap boundary = burst size * burst length.<br />

Related Information<br />

Avalon Interface Specifications<br />

Backpressure Support<br />

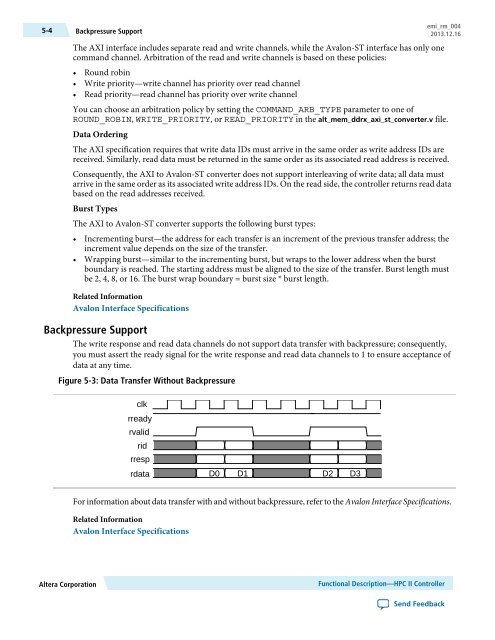

The write response and read data channels do not support data transfer with backpressure; consequently,<br />

you must assert the ready signal for the write response and read data channels to 1 to ensure acceptance of<br />

data at any time.<br />

Figure 5-3: Data Transfer Without Backpressure<br />

clk<br />

rready<br />

rvalid<br />

rid<br />

rresp<br />

rdata D0 D1 D2 D3<br />

For information about data transfer with and without backpressure, refer to the Avalon Interface Specifications.<br />

Related Information<br />

Avalon Interface Specifications<br />

<strong>Altera</strong> Corporation<br />

<strong>Functional</strong> <strong>Description</strong>—<strong>HPC</strong> <strong>II</strong> <strong>Controller</strong><br />

Send Feedback