Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

5-22<br />

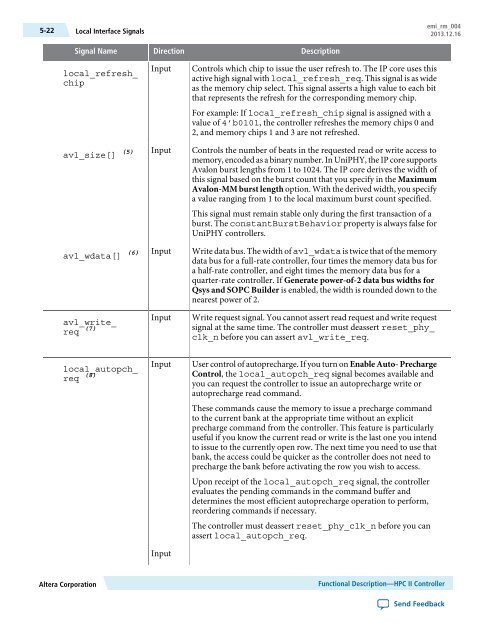

Local Interface Signals<br />

emi_rm_004<br />

2013.12.16<br />

Signal Name<br />

local_refresh_<br />

chip<br />

avl_size[] (5)<br />

avl_wdata[] (6)<br />

avl_write_<br />

req (7)<br />

Direction<br />

Input<br />

Input<br />

Input<br />

Input<br />

<strong>Description</strong><br />

Controls which chip to issue the user refresh to. The IP core uses this<br />

active high signal with local_refresh_req. This signal is as wide<br />

as the memory chip select. This signal asserts a high value to each bit<br />

that represents the refresh for the corresponding memory chip.<br />

For example: If local_refresh_chip signal is assigned with a<br />

value of 4’b0101, the controller refreshes the memory chips 0 and<br />

2, and memory chips 1 and 3 are not refreshed.<br />

Controls the number of beats in the requested read or write access to<br />

memory, encoded as a binary number. In UniPHY, the IP core supports<br />

Avalon burst lengths from 1 to 1024. The IP core derives the width of<br />

this signal based on the burst count that you specify in the Maximum<br />

Avalon-MM burst length option. With the derived width, you specify<br />

a value ranging from 1 to the local maximum burst count specified.<br />

This signal must remain stable only during the first transaction of a<br />

burst. The constantBurstBehavior property is always false for<br />

UniPHY controllers.<br />

Write data bus. The width of avl_wdata is twice that of the memory<br />

data bus for a full-rate controller, four times the memory data bus for<br />

a half-rate controller, and eight times the memory data bus for a<br />

quarter-rate controller. If Generate power-of-2 data bus widths for<br />

Qsys and SOPC Builder is enabled, the width is rounded down to the<br />

nearest power of 2.<br />

Write request signal. You cannot assert read request and write request<br />

signal at the same time. The controller must deassert reset_phy_<br />

clk_n before you can assert avl_write_req.<br />

local_autopch_<br />

req (8)<br />

Input<br />

Input<br />

User control of autoprecharge. If you turn on Enable Auto- Precharge<br />

Control, the local_autopch_req signal becomes available and<br />

you can request the controller to issue an autoprecharge write or<br />

autoprecharge read command.<br />

These commands cause the memory to issue a precharge command<br />

to the current bank at the appropriate time without an explicit<br />

precharge command from the controller. This feature is particularly<br />

useful if you know the current read or write is the last one you intend<br />

to issue to the currently open row. The next time you need to use that<br />

bank, the access could be quicker as the controller does not need to<br />

precharge the bank before activating the row you wish to access.<br />

Upon receipt of the local_autopch_req signal, the controller<br />

evaluates the pending commands in the command buffer and<br />

determines the most efficient autoprecharge operation to perform,<br />

reordering commands if necessary.<br />

The controller must deassert reset_phy_clk_n before you can<br />

assert local_autopch_req.<br />

<strong>Altera</strong> Corporation<br />

<strong>Functional</strong> <strong>Description</strong>—<strong>HPC</strong> <strong>II</strong> <strong>Controller</strong><br />

Send Feedback