Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

emi_rm_004<br />

2013.12.16<br />

<strong>Controller</strong> <strong>External</strong> Interfaces<br />

5-15<br />

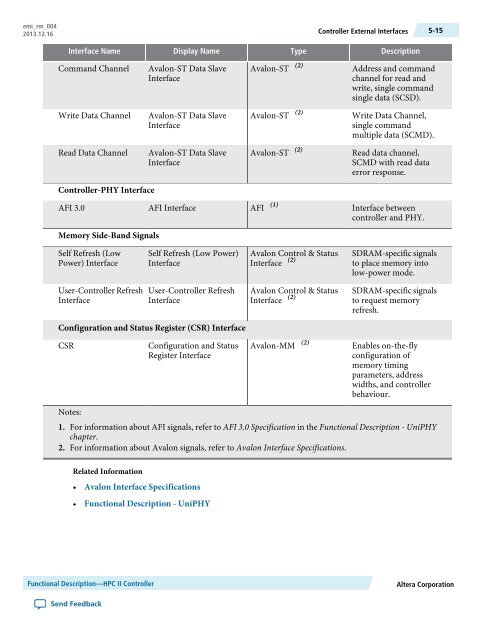

Interface Name<br />

Display Name<br />

Type<br />

<strong>Description</strong><br />

Command Channel<br />

Avalon-ST Data Slave<br />

Interface<br />

Avalon-ST (2)<br />

Address and command<br />

channel for read and<br />

write, single command<br />

single data (SCSD).<br />

Write Data Channel<br />

Avalon-ST Data Slave<br />

Interface<br />

Avalon-ST (2)<br />

Write Data Channel,<br />

single command<br />

multiple data (SCMD).<br />

Read Data Channel<br />

Avalon-ST Data Slave<br />

Interface<br />

Avalon-ST (2)<br />

Read data channel,<br />

SCMD with read data<br />

error response.<br />

<strong>Controller</strong>-PHY Interface<br />

AFI 3.0<br />

AFI Interface<br />

AFI (1)<br />

Interface between<br />

controller and PHY.<br />

<strong>Memory</strong> Side-Band Signals<br />

Self Refresh (Low<br />

Power) Interface<br />

Self Refresh (Low Power)<br />

Interface<br />

Avalon Control & Status<br />

Interface (2)<br />

SDRAM-specific signals<br />

to place memory into<br />

low-power mode.<br />

User-<strong>Controller</strong> Refresh<br />

Interface<br />

User-<strong>Controller</strong> Refresh<br />

Interface<br />

Avalon Control & Status<br />

Interface (2)<br />

SDRAM-specific signals<br />

to request memory<br />

refresh.<br />

Configuration and Status Register (CSR) Interface<br />

CSR<br />

Configuration and Status<br />

Register Interface<br />

Avalon-MM (2)<br />

Enables on-the-fly<br />

configuration of<br />

memory timing<br />

parameters, address<br />

widths, and controller<br />

behaviour.<br />

Notes:<br />

1. For information about AFI signals, refer to AFI 3.0 Specification in the <strong>Functional</strong> <strong>Description</strong> - UniPHY<br />

chapter.<br />

2. For information about Avalon signals, refer to Avalon Interface Specifications.<br />

Related Information<br />

• Avalon Interface Specifications<br />

• <strong>Functional</strong> <strong>Description</strong> - UniPHY<br />

<strong>Functional</strong> <strong>Description</strong>—<strong>HPC</strong> <strong>II</strong> <strong>Controller</strong><br />

<strong>Altera</strong> Corporation<br />

Send Feedback