Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

emi_rm_004<br />

2013.12.16<br />

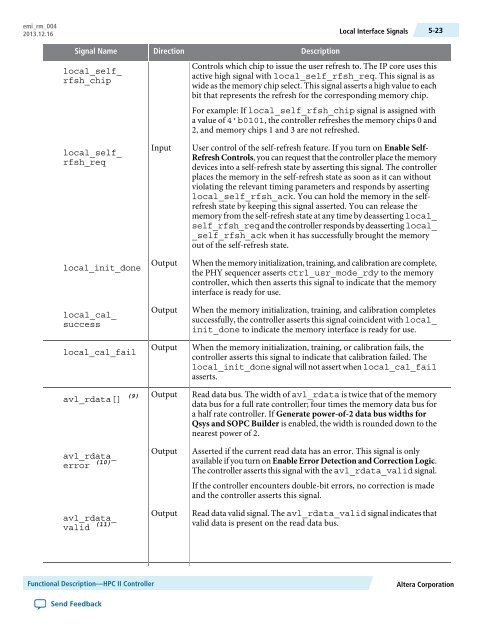

Local Interface Signals<br />

5-23<br />

Signal Name<br />

local_self_<br />

rfsh_chip<br />

local_self_<br />

rfsh_req<br />

local_init_done<br />

local_cal_<br />

success<br />

local_cal_fail<br />

avl_rdata[] (9)<br />

avl_rdata_<br />

error (10)<br />

avl_rdata_<br />

valid (11)<br />

Direction<br />

Input<br />

Output<br />

Output<br />

Output<br />

Output<br />

Output<br />

Output<br />

<strong>Description</strong><br />

Controls which chip to issue the user refresh to. The IP core uses this<br />

active high signal with local_self_rfsh_req. This signal is as<br />

wide as the memory chip select. This signal asserts a high value to each<br />

bit that represents the refresh for the corresponding memory chip.<br />

For example: If local_self_rfsh_chip signal is assigned with<br />

a value of 4’b0101, the controller refreshes the memory chips 0 and<br />

2, and memory chips 1 and 3 are not refreshed.<br />

User control of the self-refresh feature. If you turn on Enable Self-<br />

Refresh Controls, you can request that the controller place the memory<br />

devices into a self-refresh state by asserting this signal. The controller<br />

places the memory in the self-refresh state as soon as it can without<br />

violating the relevant timing parameters and responds by asserting<br />

local_self_rfsh_ack. You can hold the memory in the selfrefresh<br />

state by keeping this signal asserted. You can release the<br />

memory from the self-refresh state at any time by deasserting local_<br />

self_rfsh_req and the controller responds by deasserting local_<br />

_self_rfsh_ack when it has successfully brought the memory<br />

out of the self-refresh state.<br />

When the memory initialization, training, and calibration are complete,<br />

the PHY sequencer asserts ctrl_usr_mode_rdy to the memory<br />

controller, which then asserts this signal to indicate that the memory<br />

interface is ready for use.<br />

When the memory initialization, training, and calibration completes<br />

successfully, the controller asserts this signal coincident with local_<br />

init_done to indicate the memory interface is ready for use.<br />

When the memory initialization, training, or calibration fails, the<br />

controller asserts this signal to indicate that calibration failed. The<br />

local_init_done signal will not assert when local_cal_fail<br />

asserts.<br />

Read data bus. The width of avl_rdata is twice that of the memory<br />

data bus for a full rate controller; four times the memory data bus for<br />

a half rate controller. If Generate power-of-2 data bus widths for<br />

Qsys and SOPC Builder is enabled, the width is rounded down to the<br />

nearest power of 2.<br />

Asserted if the current read data has an error. This signal is only<br />

available if you turn on Enable Error Detection and Correction Logic.<br />

The controller asserts this signal with the avl_rdata_valid signal.<br />

If the controller encounters double-bit errors, no correction is made<br />

and the controller asserts this signal.<br />

Read data valid signal. The avl_rdata_valid signal indicates that<br />

valid data is present on the read data bus.<br />

<strong>Functional</strong> <strong>Description</strong>—<strong>HPC</strong> <strong>II</strong> <strong>Controller</strong><br />

<strong>Altera</strong> Corporation<br />

Send Feedback