Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

emi_rm_004<br />

2013.12.16<br />

<strong>Controller</strong> Interface Signals<br />

5-25<br />

Signal Name<br />

Direction<br />

<strong>Description</strong><br />

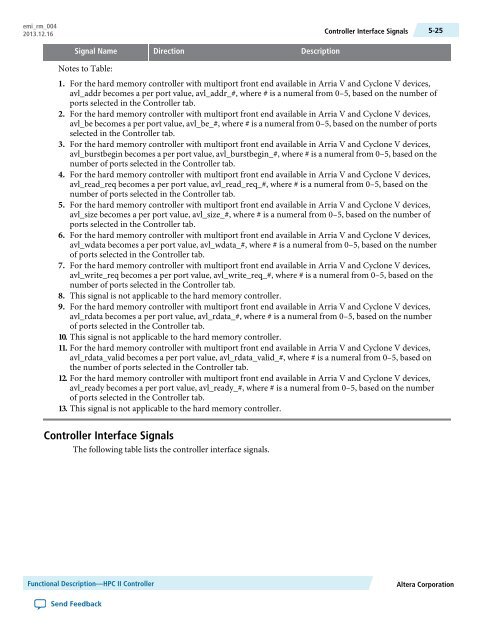

Notes to Table:<br />

1. For the hard memory controller with multiport front end available in Arria V and Cyclone V devices,<br />

avl_addr becomes a per port value, avl_addr_#, where # is a numeral from 0–5, based on the number of<br />

ports selected in the <strong>Controller</strong> tab.<br />

2. For the hard memory controller with multiport front end available in Arria V and Cyclone V devices,<br />

avl_be becomes a per port value, avl_be_#, where # is a numeral from 0–5, based on the number of ports<br />

selected in the <strong>Controller</strong> tab.<br />

3. For the hard memory controller with multiport front end available in Arria V and Cyclone V devices,<br />

avl_burstbegin becomes a per port value, avl_burstbegin_#, where # is a numeral from 0–5, based on the<br />

number of ports selected in the <strong>Controller</strong> tab.<br />

4. For the hard memory controller with multiport front end available in Arria V and Cyclone V devices,<br />

avl_read_req becomes a per port value, avl_read_req_#, where # is a numeral from 0–5, based on the<br />

number of ports selected in the <strong>Controller</strong> tab.<br />

5. For the hard memory controller with multiport front end available in Arria V and Cyclone V devices,<br />

avl_size becomes a per port value, avl_size_#, where # is a numeral from 0–5, based on the number of<br />

ports selected in the <strong>Controller</strong> tab.<br />

6. For the hard memory controller with multiport front end available in Arria V and Cyclone V devices,<br />

avl_wdata becomes a per port value, avl_wdata_#, where # is a numeral from 0–5, based on the number<br />

of ports selected in the <strong>Controller</strong> tab.<br />

7. For the hard memory controller with multiport front end available in Arria V and Cyclone V devices,<br />

avl_write_req becomes a per port value, avl_write_req_#, where # is a numeral from 0–5, based on the<br />

number of ports selected in the <strong>Controller</strong> tab.<br />

8. This signal is not applicable to the hard memory controller.<br />

9. For the hard memory controller with multiport front end available in Arria V and Cyclone V devices,<br />

avl_rdata becomes a per port value, avl_rdata_#, where # is a numeral from 0–5, based on the number<br />

of ports selected in the <strong>Controller</strong> tab.<br />

10. This signal is not applicable to the hard memory controller.<br />

11. For the hard memory controller with multiport front end available in Arria V and Cyclone V devices,<br />

avl_rdata_valid becomes a per port value, avl_rdata_valid_#, where # is a numeral from 0–5, based on<br />

the number of ports selected in the <strong>Controller</strong> tab.<br />

12. For the hard memory controller with multiport front end available in Arria V and Cyclone V devices,<br />

avl_ready becomes a per port value, avl_ready_#, where # is a numeral from 0–5, based on the number<br />

of ports selected in the <strong>Controller</strong> tab.<br />

13. This signal is not applicable to the hard memory controller.<br />

<strong>Controller</strong> Interface Signals<br />

The following table lists the controller interface signals.<br />

<strong>Functional</strong> <strong>Description</strong>—<strong>HPC</strong> <strong>II</strong> <strong>Controller</strong><br />

<strong>Altera</strong> Corporation<br />

Send Feedback