Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

5-24<br />

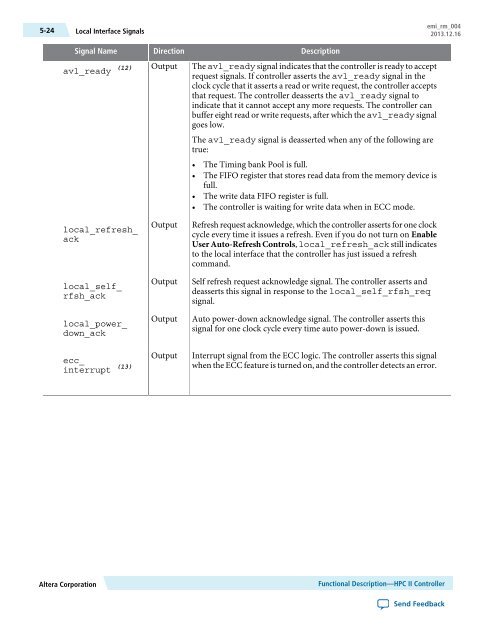

Local Interface Signals<br />

emi_rm_004<br />

2013.12.16<br />

Signal Name<br />

avl_ready (12)<br />

local_refresh_<br />

ack<br />

local_self_<br />

rfsh_ack<br />

local_power_<br />

down_ack<br />

ecc_<br />

interrupt (13)<br />

Direction<br />

Output<br />

Output<br />

Output<br />

Output<br />

Output<br />

<strong>Description</strong><br />

The avl_ready signal indicates that the controller is ready to accept<br />

request signals. If controller asserts the avl_ready signal in the<br />

clock cycle that it asserts a read or write request, the controller accepts<br />

that request. The controller deasserts the avl_ready signal to<br />

indicate that it cannot accept any more requests. The controller can<br />

buffer eight read or write requests, after which the avl_ready signal<br />

goes low.<br />

The avl_ready signal is deasserted when any of the following are<br />

true:<br />

• The Timing bank Pool is full.<br />

• The FIFO register that stores read data from the memory device is<br />

full.<br />

• The write data FIFO register is full.<br />

• The controller is waiting for write data when in ECC mode.<br />

Refresh request acknowledge, which the controller asserts for one clock<br />

cycle every time it issues a refresh. Even if you do not turn on Enable<br />

User Auto-Refresh Controls, local_refresh_ack still indicates<br />

to the local interface that the controller has just issued a refresh<br />

command.<br />

Self refresh request acknowledge signal. The controller asserts and<br />

deasserts this signal in response to the local_self_rfsh_req<br />

signal.<br />

Auto power-down acknowledge signal. The controller asserts this<br />

signal for one clock cycle every time auto power-down is issued.<br />

Interrupt signal from the ECC logic. The controller asserts this signal<br />

when the ECC feature is turned on, and the controller detects an error.<br />

<strong>Altera</strong> Corporation<br />

<strong>Functional</strong> <strong>Description</strong>—<strong>HPC</strong> <strong>II</strong> <strong>Controller</strong><br />

Send Feedback