Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

Functional Description -- HPC II Controller, External Memory ... - Altera

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

5-18<br />

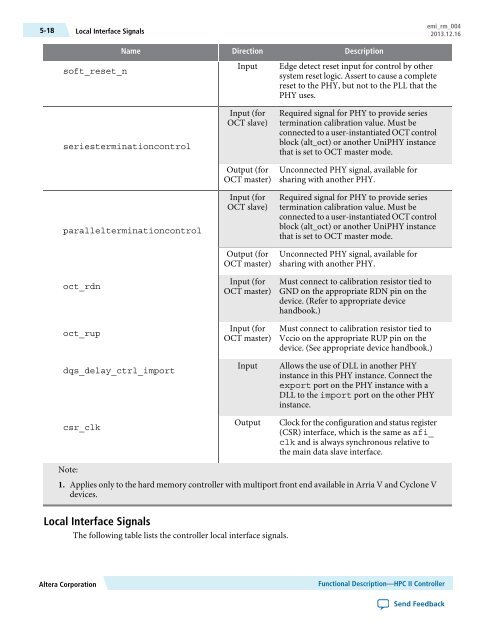

Local Interface Signals<br />

emi_rm_004<br />

2013.12.16<br />

Name<br />

soft_reset_n<br />

seriesterminationcontrol<br />

parallelterminationcontrol<br />

oct_rdn<br />

oct_rup<br />

dqs_delay_ctrl_import<br />

csr_clk<br />

Direction<br />

Input<br />

Input (for<br />

OCT slave)<br />

Output (for<br />

OCT master)<br />

Input (for<br />

OCT slave)<br />

Output (for<br />

OCT master)<br />

Input (for<br />

OCT master)<br />

Input (for<br />

OCT master)<br />

Input<br />

Output<br />

<strong>Description</strong><br />

Edge detect reset input for control by other<br />

system reset logic. Assert to cause a complete<br />

reset to the PHY, but not to the PLL that the<br />

PHY uses.<br />

Required signal for PHY to provide series<br />

termination calibration value. Must be<br />

connected to a user-instantiated OCT control<br />

block (alt_oct) or another UniPHY instance<br />

that is set to OCT master mode.<br />

Unconnected PHY signal, available for<br />

sharing with another PHY.<br />

Required signal for PHY to provide series<br />

termination calibration value. Must be<br />

connected to a user-instantiated OCT control<br />

block (alt_oct) or another UniPHY instance<br />

that is set to OCT master mode.<br />

Unconnected PHY signal, available for<br />

sharing with another PHY.<br />

Must connect to calibration resistor tied to<br />

GND on the appropriate RDN pin on the<br />

device. (Refer to appropriate device<br />

handbook.)<br />

Must connect to calibration resistor tied to<br />

Vccio on the appropriate RUP pin on the<br />

device. (See appropriate device handbook.)<br />

Allows the use of DLL in another PHY<br />

instance in this PHY instance. Connect the<br />

export port on the PHY instance with a<br />

DLL to the import port on the other PHY<br />

instance.<br />

Clock for the configuration and status register<br />

(CSR) interface, which is the same as afi_<br />

clk and is always synchronous relative to<br />

the main data slave interface.<br />

Note:<br />

1. Applies only to the hard memory controller with multiport front end available in Arria V and Cyclone V<br />

devices.<br />

Local Interface Signals<br />

The following table lists the controller local interface signals.<br />

<strong>Altera</strong> Corporation<br />

<strong>Functional</strong> <strong>Description</strong>—<strong>HPC</strong> <strong>II</strong> <strong>Controller</strong><br />

Send Feedback