Apalis Carrier Board Design Guide - Toradex

Apalis Carrier Board Design Guide - Toradex

Apalis Carrier Board Design Guide - Toradex

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

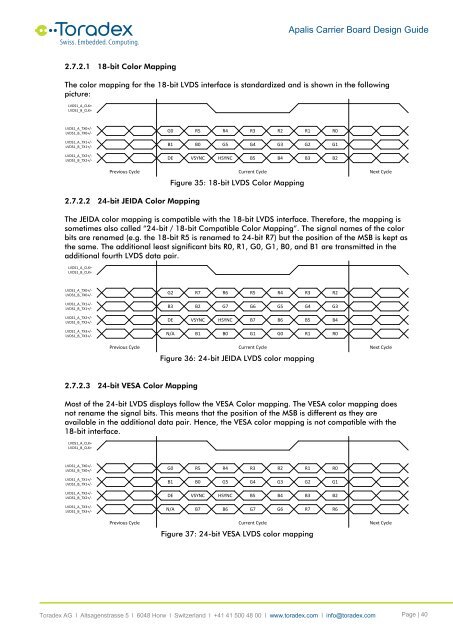

<strong>Apalis</strong> <strong>Carrier</strong> <strong>Board</strong> <strong>Design</strong> <strong>Guide</strong>2.7.2.1 18-bit Color MappingThe color mapping for the 18-bit LVDS interface is standardized and is shown in the followingpicture:LVDS1_A_CLK+LVDS1_B_CLK+G0 R5 R4 R3 R2 R1 R0B1 B0 G5 G4 G3 G2 G1DE VSYNC HSYNC B5 B4 B3 B2Previous Cycle Current Cycle Next Cycle2.7.2.2 24-bit JEIDA Color MappingFigure 35: 18-bit LVDS Color MappingThe JEIDA color mapping is compatible with the 18-bit LVDS interface. Therefore, the mapping issometimes also called “24-bit / 18-bit Compatible Color Mapping”. The signal names of the colorbits are renamed (e.g. the 18-bit R5 is renamed to 24-bit R7) but the position of the MSB is kept asthe same. The additional least significant bits R0, R1, G0, G1, B0, and B1 are transmitted in theadditional fourth LVDS data pair.LVDS1_A_CLK+LVDS1_B_CLK+G2 R7 R6 R5 R4 R3 R2B3 B2 G7 G6 G5 G4 G3DE VSYNC HSYNC B7 B6 B5 B4N/A B1 B0 G1 G0 R1 R0Previous Cycle Current Cycle Next CycleFigure 36: 24-bit JEIDA LVDS color mapping2.7.2.3 24-bit VESA Color MappingMost of the 24-bit LVDS displays follow the VESA Color mapping. The VESA color mapping doesnot rename the signal bits. This means that the position of the MSB is different as they areavailable in the additional data pair. Hence, the VESA color mapping is not compatible with the18-bit interface.LVDS1_A_CLK+LVDS1_B_CLK+LVDS1_A_TX0+/-LVDS1_B_TX0+/-LVDS1_A_TX1+/-LVDS1_B_TX1+/-LVDS1_A_TX2+/-LVDS1_B_TX2+/-LVDS1_A_TX0+/-LVDS1_B_TX0+/-LVDS1_A_TX1+/-LVDS1_B_TX1+/-LVDS1_A_TX2+/-LVDS1_B_TX2+/-LVDS1_A_TX3+/-LVDS1_B_TX3+/-LVDS1_A_TX0+/-LVDS1_B_TX0+/-LVDS1_A_TX1+/-LVDS1_B_TX1+/-LVDS1_A_TX2+/-LVDS1_B_TX2+/-LVDS1_A_TX3+/-LVDS1_B_TX3+/-G0 R5 R4 R3 R2 R1 R0B1 B0 G5 G4 G3 G2 G1DE VSYNC HSYNC B5 B4 B3 B2N/A B7 B6 G7 G6 R7 R6Previous Cycle Current Cycle Next CycleFigure 37: 24-bit VESA LVDS color mapping<strong>Toradex</strong> AG l Altsagenstrasse 5 l 6048 Horw l Switzerland l +41 41 500 48 00 l www.toradex.com l info@toradex.com Page | 40