Prüfung von Consumer-HF - beam - Elektronik & Verlag

Prüfung von Consumer-HF - beam - Elektronik & Verlag

Prüfung von Consumer-HF - beam - Elektronik & Verlag

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Aus Forschung und Technik<br />

Imec demonstrierte 3D-integrierte<br />

DRAM-on-logic für mobile Einsätze mit<br />

niedrigem Stromverbrauch<br />

imec<br />

www2.imec.be<br />

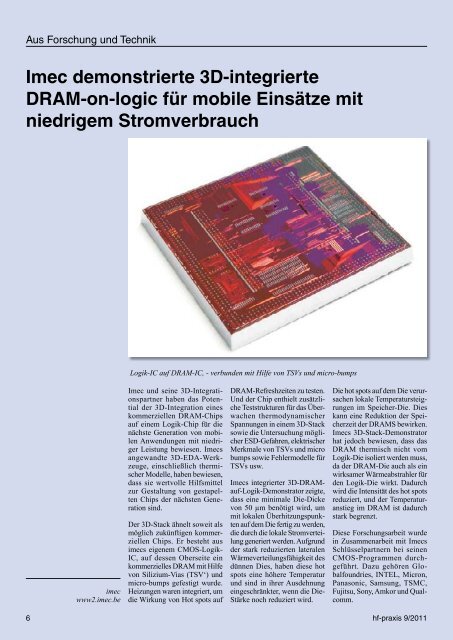

Logik-IC auf DRAM-IC, - verbunden mit Hilfe <strong>von</strong> TSVs und micro-bumps<br />

Imec und seine 3D-Integrationspartner<br />

haben das Potential<br />

der 3D-Integration eines<br />

kommerziellen DRAM-Chips<br />

auf einem Logik-Chip für die<br />

nächste Generation <strong>von</strong> mobilen<br />

Anwendungen mit niedriger<br />

Leistung bewiesen. Imecs<br />

angewandte 3D-EDA-Werkzeuge,<br />

einschließlich thermischer<br />

Modelle, haben bewiesen,<br />

dass sie wertvolle Hilfsmittel<br />

zur Gestaltung <strong>von</strong> gestapelten<br />

Chips der nächsten Generation<br />

sind.<br />

Der 3D-Stack ähnelt soweit als<br />

möglich zukünftigen kommerziellen<br />

Chips. Er besteht aus<br />

imecs eigenem CMOS-Logik-<br />

IC, auf dessen Oberseite ein<br />

kommerzielles DRAM mit Hilfe<br />

<strong>von</strong> Silizium-Vias (TSV‘) und<br />

micro-bumps gefestigt wurde.<br />

Heizungen waren integriert, um<br />

die Wirkung <strong>von</strong> Hot spots auf<br />

DRAM-Refreshzeiten zu testen.<br />

Und der Chip enthielt zusätzliche<br />

Teststrukturen für das Überwachen<br />

thermodynamischer<br />

Spannungen in einem 3D-Stack<br />

sowie die Untersuchung möglicher<br />

ESD-Gefahren, elektrischer<br />

Merkmale <strong>von</strong> TSVs und micro<br />

bumps sowie Fehlermodelle für<br />

TSVs usw.<br />

Imecs integrierter 3D-DRAMauf-Logik-Demonstrator<br />

zeigte,<br />

dass eine minimale Die-Dicke<br />

<strong>von</strong> 50 µm benötigt wird, um<br />

mit lokalen Überhitzungspunkten<br />

auf dem Die fertig zu werden,<br />

die durch die lokale Stromverteilung<br />

generiert werden. Aufgrund<br />

der stark reduzierten lateralen<br />

Wärmeverteilungsfähigkeit des<br />

dünnen Dies, haben diese hot<br />

spots eine höhere Temperatur<br />

und sind in ihrer Ausdehnung<br />

eingeschränkter, wenn die Die-<br />

Stärke noch reduziert wird.<br />

Die hot spots auf dem Die verursachen<br />

lokale Temperatursteigrungen<br />

im Speicher-Die. Dies<br />

kann eine Reduktion der Speicherzeit<br />

der DRAMS bewirken.<br />

Imecs 3D-Stack-Demonstrator<br />

hat jedoch bewiesen, dass das<br />

DRAM thermisch nicht vom<br />

Logik-Die isoliert werden muss,<br />

da der DRAM-Die auch als ein<br />

wirksamer Wärmeabstrahler für<br />

den Logik-Die wirkt. Dadurch<br />

wird die Intensität des hot spots<br />

reduziert, und der Temperaturanstieg<br />

im DRAM ist dadurch<br />

stark begrenzt.<br />

Diese Forschungsarbeit wurde<br />

in Zusammenarbeit mit Imecs<br />

Schlüsselpartnern bei seinen<br />

CMOS-Programmen durchgeführt.<br />

Dazu gehören Globalfoundries,<br />

INTEL, Micron,<br />

Panasonic, Samsung, TSMC,<br />

Fujitsu, Sony, Amkor und Qualcomm.<br />

6 hf-praxis 9/2011