mitac 8599.pdf - tim.id.au

mitac 8599.pdf - tim.id.au

mitac 8599.pdf - tim.id.au

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

8<br />

8<br />

7<br />

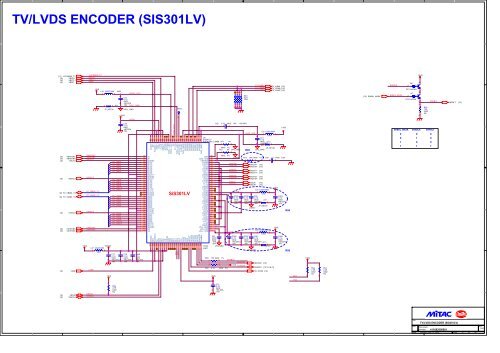

TV/LVDS ENCODER (SIS301LV)<br />

7<br />

6<br />

6<br />

5<br />

D D<br />

[11] 14.318MHZ_TV<br />

[6] VBCLK<br />

[6] VBCTL1<br />

[6] VBDE<br />

14.318MHZ_TV<br />

VBCLK<br />

VBCTL1<br />

VBDE<br />

+3VS<br />

L35 120Z/100M 1608<br />

1 2<br />

1 2 JL9<br />

JP_NET20<br />

1<br />

2<br />

+3VS<br />

1<br />

2<br />

+TVPLL_VCC<br />

C74<br />

0.1U<br />

0402<br />

+80-20%<br />

16V TVPLL_GND<br />

+1.8VS<br />

1<br />

2<br />

1<br />

2<br />

TVPLL_GND<br />

+VDDV<br />

1<br />

2<br />

MOD_XOUT<br />

64<br />

63<br />

62<br />

61<br />

60<br />

59<br />

58<br />

57<br />

56<br />

55<br />

54<br />

53<br />

52<br />

51<br />

50<br />

49<br />

48<br />

47<br />

46<br />

45<br />

44<br />

43<br />

42<br />

41<br />

40<br />

39<br />

DVDD1<br />

DE1<br />

FLD/STL1<br />

VREF1<br />

VDDV<br />

P-OUT<br />

RESET*<br />

GPIO[5]<br />

GPIO[4]<br />

TVPLL_VDD<br />

TVPLL_VCC<br />

XO<br />

XI / FIN<br />

TVPLL_GND<br />

BCO/VSYNC<br />

C/HSYNC<br />

DAC_GND0<br />

DACA[3]<br />

DACB[3]<br />

DACA[2[<br />

DACB[2]<br />

DACA[1]<br />

DACB[1]<br />

DACA[0]<br />

DACB[0]<br />

DAC_GND1<br />

DVDD0<br />

DE2<br />

FLD/STL2<br />

AS<br />

SPD<br />

SPC<br />

HIN<br />

VIN<br />

VREF2<br />

SDD<br />

SDC<br />

DD1<br />

DC1<br />

DD2<br />

DC2<br />

V5V<br />

HOUT<br />

VOUT<br />

HPD<br />

HPINT*<br />

GPIO[0]<br />

GPIO[1]<br />

GPIO[2]<br />

GPIO[3]<br />

ENAVDD<br />

ENABKL<br />

103<br />

104<br />

105<br />

106<br />

107<br />

108<br />

109<br />

110<br />

111<br />

112<br />

113<br />

114<br />

115<br />

116<br />

117<br />

118<br />

119<br />

120<br />

121<br />

122<br />

123<br />

124<br />

125<br />

126<br />

127<br />

128<br />

DD2<br />

DC2<br />

TP510<br />

1<br />

+5VS<br />

1<br />

5<br />

1<br />

2<br />

4<br />

3<br />

2<br />

1<br />

5<br />

6<br />

7<br />

8<br />

1<br />

2<br />

1<br />

2<br />

RP4<br />

75*4<br />

1206<br />

C76<br />

C62 0.1U 0402 16V +80-20%<br />

C<br />

0.1U<br />

0402<br />

1 2<br />

+3VS<br />

C<br />

+80-20%<br />

16V<br />

+DAC_VDD<br />

L32 120Z/100M<br />

1 2<br />

1608<br />

ENBKL_MASK<br />

0<br />

ENABLK<br />

0<br />

ENPBLT<br />

0<br />

U9<br />

SIS301LV<br />

PQFP128A_0.5MM R71 147<br />

1 2<br />

0603 1%<br />

R72 6K DAC_GND<br />

1 2<br />

R0C<br />

C73<br />

0.1U<br />

0402 JL10<br />

+80-20% 1 2<br />

16V<br />

JP_NET20<br />

DAC_GND<br />

0<br />

1<br />

1<br />

1<br />

0<br />

1<br />

0<br />

0<br />

1<br />

B<br />

[6] VBVSYNC<br />

[6] VBHSYNC<br />

[6] VBCTL0<br />

[6] VBGCLK<br />

[6] FC_VBD[0..11]<br />

[6] FC_VAD[0..11]<br />

[6] VAGCLK<br />

[6] VAHSYNC<br />

[6] VAVSYNC<br />

VBVSYNC<br />

VBHSYNC<br />

VBCTL0<br />

VBGCLK<br />

FC_VBD[0..11]<br />

FC_VAD[0..11]<br />

VAGCLK<br />

VAHSYNC<br />

VAVSYNC<br />

FC_VBD0<br />

FC_VBD1<br />

FC_VBD2<br />

FC_VBD3<br />

FC_VBD4<br />

FC_VBD5<br />

FC_VBD6<br />

FC_VBD7<br />

FC_VBD8<br />

FC_VBD9<br />

FC_VBD10<br />

FC_VBD11<br />

FC_VAD0<br />

FC_VAD1<br />

FC_VAD2<br />

FC_VAD3<br />

FC_VAD4<br />

FC_VAD5<br />

FC_VAD6<br />

FC_VAD7<br />

FC_VAD8<br />

FC_VAD9<br />

FC_VAD10<br />

FC_VAD11<br />

65<br />

V1<br />

66<br />

H1<br />

67<br />

DGND3<br />

68<br />

D1[0]<br />

69<br />

D1[1]<br />

70<br />

D1[2]<br />

71<br />

D1[3]<br />

72<br />

D1[4]<br />

73<br />

D1[5]<br />

74<br />

XCLK1*<br />

75<br />

DGND2<br />

76<br />

XCLK1<br />

77<br />

D1[6]<br />

78<br />

D1[7]<br />

79<br />

D1[8]<br />

80<br />

D1[9]<br />

81<br />

D1[10]<br />

82<br />

D1[11]<br />

83<br />

DVDD3<br />

84<br />

DVDD2<br />

85<br />

D2[0]<br />

86<br />

D2[1]<br />

87<br />

D2[2]<br />

88<br />

D2[3]<br />

89<br />

D2[4]<br />

90<br />

D2[5]<br />

91<br />

XCLK2*<br />

92<br />

DGND1<br />

93<br />

XCLK2<br />

94<br />

D2[6]<br />

95<br />

D2[7]<br />

96<br />

D2[8]<br />

97<br />

D2[9]<br />

98<br />

D2[10]<br />

99<br />

D2[11]<br />

100<br />

DGND0<br />

101<br />

H2<br />

102<br />

V2<br />

SiS301LV<br />

ISET<br />

38<br />

DAC_VDD<br />

37<br />

VSWING<br />

36<br />

LGND5<br />

35<br />

LDC0*<br />

34<br />

LDC0<br />

33<br />

LVDD5<br />

32<br />

LDC1*<br />

31<br />

LDC1<br />

30<br />

LGND4<br />

29<br />

LDC2*<br />

28<br />

LDC2<br />

27<br />

LVDD4<br />

26<br />

LL1C*<br />

25<br />

LL1C<br />

24<br />

LGND3<br />

23<br />

LDC3*<br />

22<br />

LDC3<br />

21<br />

LVDD3<br />

20<br />

LVDD2<br />

19<br />

LDC4*<br />

18<br />

LDC4<br />

17<br />

LGND2<br />

16<br />

LDC5*<br />

15<br />

LDC5<br />

14<br />

LVDD1<br />

13<br />

LDC6*<br />

12<br />

LDC6<br />

11<br />

LGND1<br />

10<br />

LDC7*<br />

9<br />

LDC7<br />

8<br />

LVDD0<br />

7<br />

LL2C*<br />

6<br />

LL2C<br />

5<br />

LGND0<br />

4<br />

LPLL_GND<br />

3<br />

LPLLCAP<br />

2<br />

LPLL_VDD<br />

1<br />

0603 5%<br />

LGND1 R73 24K 0402 1% C50 1U 0402 6.3V<br />

1 2<br />

1 2<br />

TXOUT0-<br />

TXOUT0- [10]<br />

TXOUT0+<br />

TXOUT0+ [10]<br />

TXOUT1-<br />

TXOUT1- [10]<br />

TXOUT1+<br />

TXOUT1+ [10]<br />

TXOUT2-<br />

TXOUT2- [10]<br />

TXOUT2+<br />

TXOUT2+ [10]<br />

TXCLK-<br />

TXCLK- [10]<br />

TXCLK+<br />

TXCLK+ [10]<br />

+3VS<br />

L30 120Z/100M<br />

+LVDD<br />

1 2<br />

1608<br />

C535 C536 C55<br />

C403<br />

0.1U 0.1U 0.1U<br />

0.1U<br />

0402 0402 0402 JL11<br />

0402<br />

+80-20% +80-20% +80-20% 1 2<br />

+80-20%<br />

16V 16V 16V<br />

16V<br />

JP_NET20<br />

LGND1<br />

R06<br />

+3VS<br />

L28 120Z/100M<br />

+LPLL_VDD<br />

1 2<br />

1608<br />

B<br />

C57<br />

100P<br />

C350<br />

0.1U<br />

C537<br />

0.1U<br />

C56<br />

0.1U<br />

C405<br />

0.1U<br />

0402<br />

0402 0402 0402<br />

0402<br />

+3VS<br />

+DVDD<br />

14x20<br />

10%<br />

50V<br />

LPLLGND<br />

+80-20%<br />

16V<br />

+80-20%<br />

16V<br />

+80-20% JL13<br />

16V 1 2<br />

JP_NET20<br />

+80-20%<br />

16V<br />

L37 120Z/100M<br />

1 2<br />

1608<br />

LQFP<br />

LPLLGND<br />

R06<br />

C77 C78 C406<br />

0.1U<br />

0402<br />

0.1U<br />

0402<br />

0.1U<br />

0402<br />

R83 100 0402 1%<br />

+3VS<br />

+80-20%<br />

16V<br />

+80-20%<br />

16V<br />

+80-20%<br />

16V<br />

1<br />

1<br />

R90 4.7K<br />

2 ENABLK<br />

ENAVDD<br />

2<br />

+3VS<br />

PCIRST#<br />

0402 5%<br />

ENAVDD [10]<br />

PCIRST# [12,15,16,21]<br />

R92 R91<br />

[6] VADE<br />

VADE<br />

PCI_INTA# [12]<br />

2.2K<br />

0402<br />

2.2K<br />

0402<br />

5%<br />

5%<br />

1<br />

C72<br />

A<br />

[6]<br />

[6]<br />

VBCAD<br />

VBHCLK<br />

VBCAD<br />

VBHCLK<br />

R99<br />

4.7K<br />

0402<br />

5%<br />

0.1U<br />

0402<br />

+80-20%<br />

16V<br />

A<br />

2<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

1<br />

2<br />

TV_LUMA<br />

TV_CRMA<br />

TV_COMP<br />

1<br />

2<br />

4<br />

TV_LUMA [10]<br />

TV_CRMA [10]<br />

TV_COMP [10]<br />

1<br />

2<br />

1<br />

2<br />

4<br />

DD2<br />

DC2<br />

1<br />

2<br />

1<br />

2<br />

3<br />

3<br />

[13]<br />

ENBKL_MASK<br />

2<br />

ENABLK<br />

ENBKL_MASK<br />

2<br />

Q6<br />

2 R1<br />

DTC144TKA<br />

Title<br />

1 31<br />

3<br />

Q7<br />

2 R1<br />

DTC144TKA<br />

+5VS<br />

1<br />

2<br />

R93<br />

10K<br />

0402<br />

5%<br />

ENPBLT<br />

TV/LVDS ENCODER (SIS301LV)<br />

Size<br />

Document<br />

Number 411682900001<br />

Rev<br />

R06<br />

Date: Monday, April 12, 2004<br />

Sheet<br />

1<br />

8 of 28<br />

1<br />

ENPBLT [10]