mitac 8599.pdf - tim.id.au

mitac 8599.pdf - tim.id.au

mitac 8599.pdf - tim.id.au

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

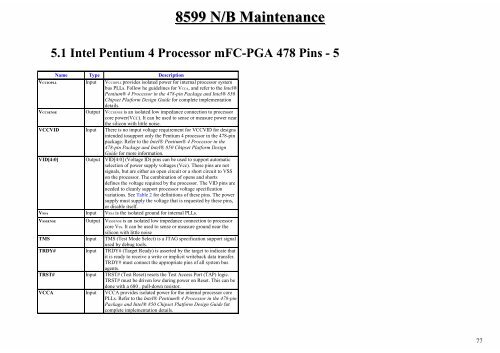

Name Type Description<br />

VCCIOPLL<br />

Input VCCIOPLL prov<strong>id</strong>es isolated power for internal processor system<br />

bus PLLs. Follow he gu<strong>id</strong>elines for VCCA, and refer to the Intel®<br />

Pentium® 4 Processor in the 478-pin Package and Intel® 850<br />

Chipset Platform Design Gu<strong>id</strong>e for complete implementation<br />

details.<br />

VCCSENSE<br />

Output VCCSENSE is an isolated low impedance connection to processor<br />

core power(VCC). It can be used to sense or measure power near<br />

the silicon with little noise.<br />

VCCVID Input There is no imput voltage requirement for VCCVID for designs<br />

intended tosupport only the Pentium 4 processor in the 478-pin<br />

package. Refer to the Intel® Pentium® 4 Processor in the<br />

478-pin Package and Intel® 850 Chipset Platform Design<br />

Gu<strong>id</strong>e for more information.<br />

VID[4:0]<br />

Output VID[4:0] (Voltage ID) pins can be used to support <strong>au</strong>tomatic<br />

selection of power supply voltages (Vcc). These pins are not<br />

signals, but are either an open circuit or a short circuit to VSS<br />

on the processor. The combination of opens and shorts<br />

defines the voltage required by the processor. The VID pins are<br />

needed to cleanly support processor voltage specification<br />

variations. See Table 2 for definitions of these pins. The power<br />

supply must supply the voltage that is requested by these pins,<br />

or disable itself.<br />

VSSA Input VSSA is the isolated ground for internal PLLs.<br />

VSSSENSE<br />

Output VSSSENSE is an isolated low impedance connection to processor<br />

core VSS. It can be used to sense or measure ground near the<br />

silicon with little noise<br />

TMS Input TMS (Test Mode Select) is a JTAG specification support signal<br />

TRDY#<br />

TRST#<br />

VCCA<br />

Input<br />

Input<br />

used by debug tools.<br />

TRDY# (Target Ready) is asserted by the target to indicate that<br />

it is ready to receive a write or implicit writeback data transfer.<br />

TRDY# must connect the appropriate pins of all system bus<br />

agents.<br />

TRST# (Test Reset) resets the Test Access Port (TAP) logic.<br />

TRST# must be driven low during power on Reset. This can be<br />

done with a 680 . pull-down resistor.<br />

8599 N/B Maintenance<br />

5.1 Intel Pentium 4 Processor mFC-PGA 478 Pins - 5<br />

Input<br />

VCCA prov<strong>id</strong>es isolated power for the internal processor core<br />

PLLs. Refer to the Intel® Pentium® 4 Processor in the 478-pin<br />

Package and Intel® 850 Chipset Platform Design Gu<strong>id</strong>e for<br />

complete implementation details.<br />

77