mitac 8599.pdf - tim.id.au

mitac 8599.pdf - tim.id.au

mitac 8599.pdf - tim.id.au

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

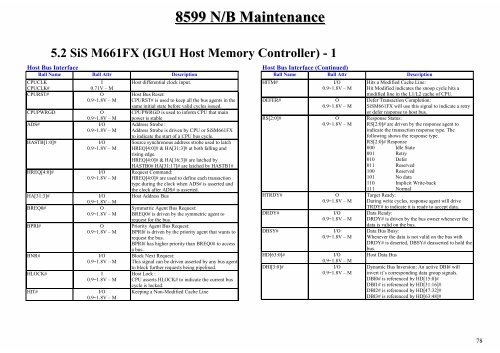

8599 N/B Maintenance<br />

5.2 SiS M661FX (IGUI Host Memory Controller) - 1<br />

Host Bus Interface<br />

Ball Name Ball Attr Description<br />

CPUCLK<br />

I<br />

CPUCLK#<br />

0.71V – M<br />

CPURST# O<br />

0.9~1.8V – M<br />

CPUPWRGD O<br />

0.9~1.8V – M<br />

ADS# I/O<br />

0.9~1.8V – M<br />

HASTB[1:0]# I/O<br />

0.9~1.8V – M<br />

HREQ[4:0]# I/O<br />

0.9~1.8V – M<br />

HA[31:3]# I/O<br />

0.9~1.8V – M<br />

BREQ0# O<br />

0.9~1.8V – M<br />

BPRI# O<br />

0.9~1.8V – M<br />

BNR# I/O<br />

0.9~1.8V – M<br />

HLOCK# I<br />

0.9~1.8V – M<br />

HIT# I/O<br />

0.9~1.8V – M<br />

Host differential clock input.<br />

Host Bus Reset:<br />

CPURST# is used to keep all the bus agents in the<br />

same initial state before val<strong>id</strong> cycles issued.<br />

CPUPWRGD is used to inform CPU that main<br />

power is stable<br />

Address Strobe :<br />

Address Strobe is driven by CPU or SiSM661FX<br />

to indicate the start of a CPU bus cycle.<br />

Source synchronous address strobe used to latch<br />

HREQ[4:0]# & HA[31:3]# at both falling and<br />

rising edge.<br />

HREQ[4:0]# & HA[16:3]# are latched by<br />

HASTB0# HA[31:17]# are latched by HASTB1#<br />

Request Command:<br />

HREQ[4:0]# are used to define each transaction<br />

type during the clock when ADS# is asserted and<br />

the clock after ADS# is asserted.<br />

Host Address Bus<br />

Symmetric Agent Bus Request:<br />

BREQ0# is driven by the symmetric agent to<br />

request for the bus.<br />

Priority Agent Bus Request:<br />

BPRI# is driven by the priority agent that wants to<br />

request the bus.<br />

BPRI# has higher priority than BREQ0# to access<br />

a bus.<br />

Block Next Request:<br />

This signal can be driven asserted by any bus agent<br />

to block further requests being pipelined.<br />

Host Lock :<br />

CPU asserts HLOCK# to indicate the current bus<br />

cycle is locked.<br />

Keeping a Non-Modified Cache Line<br />

Host Bus Interface (Continued)<br />

Ball Name Ball Attr Description<br />

HITM# I/O<br />

0.9~1.8V – M<br />

DEFER# O<br />

0.9~1.8V – M<br />

RS[2:0]# O<br />

0.9~1.8V – M<br />

HTRDY# O<br />

0.9~1.8V – M<br />

DRDY# I/O<br />

0.9~1.8V – M<br />

DBSY# I/O<br />

0.9~1.8V – M<br />

HD[63:0]# I/O<br />

0.9~1.8V – M<br />

DBI[3:0]# I/O<br />

0.9~1.8V – M<br />

Hits a Modified Cache Line:<br />

Hit Modified indicates the snoop cycle hits a<br />

modified line in the L1/L2 cache of CPU.<br />

Defer Transaction Completion:<br />

SiSM661FX will use this signal to indicate a retry<br />

or defer response to host bus.<br />

Response Status:<br />

RS[2:0]# are driven by the response agent to<br />

indicate the transaction response type. The<br />

following shows the response type.<br />

RS[2:0]# Response<br />

000 Idle State<br />

001 Retry<br />

010 Defer<br />

011 Reserved<br />

100 Reserved<br />

101 No data<br />

110 Implicit Write-back<br />

111 Normal<br />

Target Ready:<br />

During write cycles, response agent will drive<br />

TRDY# to indicate it is ready to accept data.<br />

Data Ready:<br />

DRDY# is driven by the bus owner whenever the<br />

data is val<strong>id</strong> on the bus.<br />

Data Bus Busy:<br />

Whenever the data is not val<strong>id</strong> on the bus with<br />

DRDY# is deserted, DBSY# deasserted to hold the<br />

bus.<br />

Host Data Bus<br />

Dynamic Bus Inversion: An active DBI# will<br />

invert it’s corresponding data group signals.<br />

DBI0# is referenced by HD[15:0]#<br />

DBI1# is referenced by HD[31:16]#<br />

DBI2# is referenced by HD[47:32]#<br />

DBI3# is referenced by HD[63:48]#<br />

78