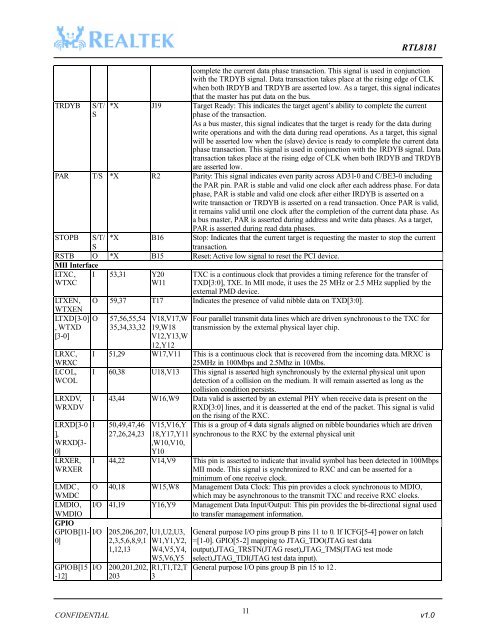

RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>RTL8181</strong>TRDYBS/T/Scomplete the current data phase transaction. This signal is used in conjunctionwith the TRDYB signal. Data transaction takes place at the rising edge of CLKwhen both IRDYB and TRDYB are asserted low. As a target, this signal indicatesthat the master has put data on the bus.*X J19 Target Ready: This indicates the target agent’s ability to complete the currentphase of the transaction.As a bus master, this signal indicates that the target is ready for the data duringwrite operations and with the data during read operations. As a target, this signalwill be asserted low when the (slave) device is ready to complete the current dataphase transaction. This signal is used in conjunction with the IRDYB signal. Datatransaction takes place at the rising edge of CLK when both IRDYB and TRDYBare asserted low.PAR T/S *X R2 Parity: This signal indicates even parity across AD31-0 and C/BE3-0 includingthe PAR pin. PAR is stable and valid one clock after each address phase. For dataphase, PAR is stable and valid one clock after either IRDYB is asserted on awrite transaction or TRDYB is asserted on a read transaction. Once PAR is valid,it remains valid until one clock after the completion of the current data phase. Asa bus master, PAR is asserted during address and write data phases. As a target,PAR is asserted during read data phases.STOPB S/T/S*X B16 Stop: Indicates that the current target is requesting the master to stop the currenttransaction.RSTB O *X B15 Reset: Active low signal to reset the PCI device.MII InterfaceLTXC,WTXCI 53,31 Y20W11TXC is a continuous clock that provides a timing reference for the transfer ofTXD[3:0], TXE. In MII mode, it uses the 25 MHz or 2.5 MHz supplied by theexternal PMD device.LTXEN, O 59,37 T17 Indicates the presence of valid nibble data on TXD[3:0].WTXENLTXD[3-0] O 57,56,55,54 V18,V17,W Four parallel transmit data lines which are driven synchronous to the TXC for, WTXD 35,34,33,32 19,W18 transmission by the external physical layer chip.[3-0]V12,Y13,W12,Y12LRXC,WRXCI 51,29 W17,V11 This is a continuous clock that is recovered from the incoming data. MRXC is25MHz in 100Mbps and 2.5Mhz in 10Mbs.LCOL,WCOLI 60,38 U18,V13 This signal is asserted high synchronously by the external physical unit upondetection of a collision on the medium. It will remain asserted as long as theLRXDV,WRXDVLRXD[3-0],WRXD[3-0]LRXER,WRXERcollision condition persists.I 43,44 W16,W9 Data valid is asserted by an external PHY when receive data is present on theRXD[3:0] lines, and it is deasserted at the end of the packet. This signal is validon the rising of the RXC.I 50,49,47,4627,26,24,23V15,V16,Y18,Y17,Y11,W10,V10,Y10This is a group of 4 data signals aligned on nibble boundaries which are drivensynchronous to the RXC by the external physical unitI 44,22 V14,V9 This pin is asserted to indicate that invalid symbol has been detected in 100MbpsMII mode. This signal is synchronized to RXC and can be asserted for aminimum of one receive clock.LMDC,WMDCLMDIO,WMDIOGPIOGPIOB[11- I/O 205,206,207,0]2,3,5,6,8,9,11,12,13GPIOB[15-12]O 40,18 W15,W8 Management Data Clock: This pin provides a clock synchronous to MDIO,which may be asynchronous to the transmit TXC and receive RXC clocks.I/O 41,19 Y16,Y9 Management Data Input/Output: This pin provides the bi-directional signal usedto transfer management information.I/O 200,201,202,203U1,U2,U3,W1,Y1,Y2,W4,V5,Y4,W5,V6,Y5R1,T1,T2,T3General purpose I/O pins group B pins 11 to 0. If ICFG[5-4] power on latch=[1-0]. GPIO[5-2] mapping to JTAG_TDO(JTAG test dataoutput),JTAG_TRSTN(JTAG reset),JTAG_TMS(JTAG test modeselect),JTAG_TDI(JTAG test data input).General purpose I/O pins group B pin 15 to 12.11CONFIDENTIAL v1.0