RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

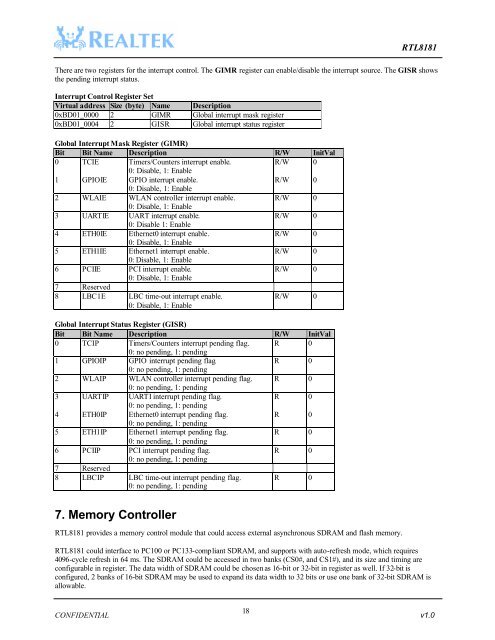

<strong>RTL8181</strong>There are two registers for the interrupt control. The GIMR register can enable/disable the interrupt source. The GISR showsthe pending interrupt status.Interrupt Control Register SetVirtual address Size (byte) Name Description0xBD01_0000 2 GIMR Global interrupt mask register0xBD01_0004 2 GISR Global interrupt status registerGlobal Interrupt Mask Register (GIMR)Bit Bit Name Description R/W InitVal0 TCIE Timers/Counters interrupt enable.R/W 00: Disable, 1: Enable1 GPIOIE GPIO interrupt enable.R/W 00: Disable, 1: Enable2 WLAIE W<strong>LAN</strong> controller interrupt enable.R/W 00: Disable, 1: Enable3 UARTIE UART interrupt enable.R/W 00: Disable 1: Enable4 ETH0IE Ethernet0 interrupt enable.R/W 00: Disable, 1: Enable5 ETH1IE Ethernet1 interrupt enable.R/W 00: Disable, 1: Enable6 PCIIE PCI interrupt enable.R/W 00: Disable, 1: Enable7 Reserved8 LBC1E LBC time-out interrupt enable.0: Disable, 1: EnableR/W 0Global Interrupt Status Register (GISR)Bit Bit Name Description R/W InitVal0 TCIP Timers/Counters interrupt pending flag. R 00: no pending, 1: pending1 GPIOIP GPIO interrupt pending flag.R 00: no pending, 1: pending2 WLAIP W<strong>LAN</strong> controller interrupt pending flag. R 00: no pending, 1: pending3 UARTIP UARTI interrupt pending flag.R 00: no pending, 1: pending4 ETH0IP Ethernet0 interrupt pending flag.R 00: no pending, 1: pending5 ETH1IP Ethernet1 interrupt pending flag.R 00: no pending, 1: pending6 PCIIP PCI interrupt pending flag.R 00: no pending, 1: pending7 Reserved8 LBCIP LBC time-out interrupt pending flag.0: no pending, 1: pendingR 07. Memory <strong>Controller</strong><strong>RTL8181</strong> provides a memory control module that could access external asynchronous SDRAM and flash memory.<strong>RTL8181</strong> could interface to PC100 or PC133-compliant SDRAM, and supports with auto-refresh mode, which requires4096-cycle refresh in 64 ms. The SDRAM could be accessed in two banks (CS0#, and CS1#), and its size and timing areconfigurable in register. The data width of SDRAM could be chosen as 16-bit or 32-bit in register as well. If 32-bit isconfigured, 2 banks of 16-bit SDRAM may be used to expand its data width to 32 bits or use one bank of 32-bit SDRAM isallowable.18CONFIDENTIAL v1.0