RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

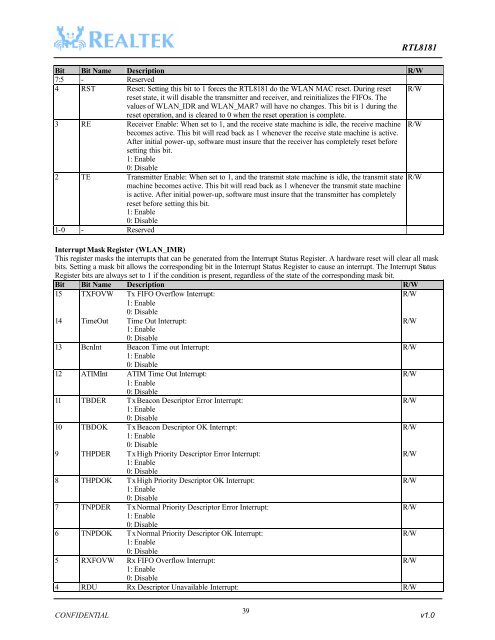

<strong>RTL8181</strong>Bit Bit Name Description R/W7:5 - Reserved4 RST Reset: Setting this bit to 1 forces the <strong>RTL8181</strong> do the W<strong>LAN</strong> MAC reset. During reset R/Wreset state, it will disable the transmitter and receiver, and reinitializes the FIFOs. Thevalues of W<strong>LAN</strong>_IDR and W<strong>LAN</strong>_MAR7 will have no changes. This bit is 1 during thereset operation, and is cleared to 0 when the reset operation is complete.3 RE Receiver Enable: When set to 1, and the receive state machine is idle, the receive machine R/Wbecomes active. This bit will read back as 1 whenever the receive state machine is active.After initial power-up, software must insure that the receiver has completely reset beforesetting this bit.1: Enable0: Disable2 TE Transmitter Enable: When set to 1, and the transmit state machine is idle, the transmit state R/Wmachine becomes active. This bit will read back as 1 whenever the transmit state machineis active. After initial power-up, software must insure that the transmitter has completelyreset before setting this bit.1: Enable0: Disable1-0 - ReservedInterrupt Mask Register (W<strong>LAN</strong>_IMR)This register masks the interrupts that can be generated from the Interrupt Status Register. A hardware reset will clear all maskbits. Setting a mask bit allows the corresponding bit in the Interrupt Status Register to cause an interrupt. The Interrupt StatusRegister bits are always set to 1 if the condition is present, regardless of the state of the corresponding mask bit.Bit Bit Name Description R/W15 TXFOVW Tx FIFO Overflow Interrupt:R/W1: Enable0: Disable14 TimeOut Time Out Interrupt:R/W1: Enable0: Disable13 BcnInt Beacon Time out Interrupt:R/W1: Enable0: Disable12 ATIMInt ATIM Time Out Interrupt:R/W1: Enable0: Disable11 TBDER Tx Beacon Descriptor Error Interrupt:R/W1: Enable0: Disable10 TBDOK Tx Beacon Descriptor OK Interrupt:R/W1: Enable0: Disable9 THPDER Tx High Priority Descriptor Error Interrupt:R/W1: Enable0: Disable8 THPDOK Tx High Priority Descriptor OK Interrupt:R/W1: Enable0: Disable7 TNPDER Tx Normal Priority Descriptor Error Interrupt:R/W1: Enable0: Disable6 TNPDOK Tx Normal Priority Descriptor OK Interrupt:R/W1: Enable0: Disable5 RXFOVW Rx FIFO Overflow Interrupt:R/W1: Enable0: Disable4 RDU Rx Descriptor Unavailable Interrupt: R/W39CONFIDENTIAL v1.0