RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

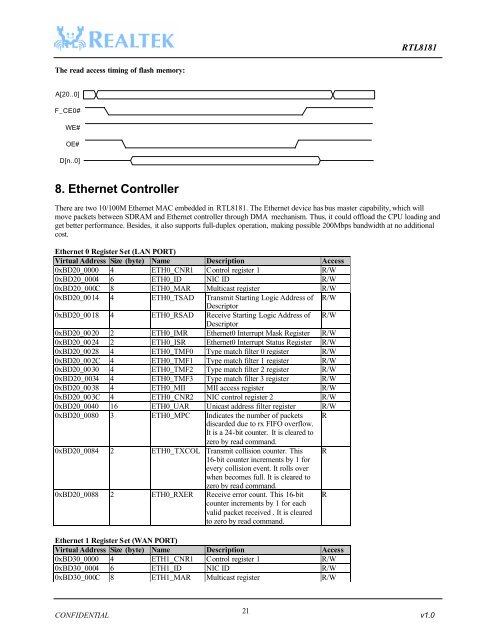

<strong>RTL8181</strong>The read access timing of flash memory:A[20..0]F_CE0#WE#OE#D[n..0]8. Ethernet <strong>Controller</strong>There are two 10/100M Ethernet MAC embedded in <strong>RTL8181</strong>. The Ethernet device has bus master capability, which willmove packets between SDRAM and Ethernet controller through DMA mechanism. Thus, it could offload the CPU loading andget better performance. Besides, it also supports full-duplex operation, making possible 200Mbps bandwidth at no additionalcost.Ethernet 0 Register Set (<strong>LAN</strong> PORT)Virtual Address Size (byte) Name Description <strong>Access</strong>0xBD20_0000 4 ETH0_CNR1 Control register 1 R/W0xBD20_0004 6 ETH0_ID NIC ID R/W0xBD20_000C 8 ETH0_MAR Multicast register R/W0xBD20_0014 4 ETH0_TSAD Transmit Starting Logic Address of R/WDescriptor0xBD20_0018 4 ETH0_RSAD Receive Starting Logic Address of R/WDescriptor0xBD20_0020 2 ETH0_IMR Ethernet0 Interrupt Mask Register R/W0xBD20_0024 2 ETH0_ISR Ethernet0 Interrupt Status Register R/W0xBD20_0028 4 ETH0_TMF0 Type match filter 0 register R/W0xBD20_002C 4 ETH0_TMF1 Type match filter 1 register R/W0xBD20_0030 4 ETH0_TMF2 Type match filter 2 register R/W0xBD20_0034 4 ETH0_TMF3 Type match filter 3 register R/W0xBD20_0038 4 ETH0_MII MII access register R/W0xBD20_003C 4 ETH0_CNR2 NIC control register 2 R/W0xBD20_0040 16 ETH0_UAR Unicast address filter register R/W0xBD20_0080 3 ETH0_MPC Indicates the number of packets Rdiscarded due to rx FIFO overflow.It is a 24-bit counter. It is cleared tozero by read command.0xBD20_0084 2 ETH0_TXCOL Transmit collision counter. This R16-bit counter increments by 1 forevery collision event. It rolls overwhen becomes full. It is cleared tozero by read command.0xBD20_0088 2 ETH0_RXER Receive error count. This 16-bitcounter increments by 1 for eachvalid packet received . It is clearedto zero by read command.REthernet 1 Register Set (WAN PORT)Virtual Address Size (byte) Name Description <strong>Access</strong>0xBD30_0000 4 ETH1_CNR1 Control register 1 R/W0xBD30_0004 6 ETH1_ID NIC ID R/W0xBD30_000C 8 ETH1_MAR Multicast register R/W21CONFIDENTIAL v1.0