RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

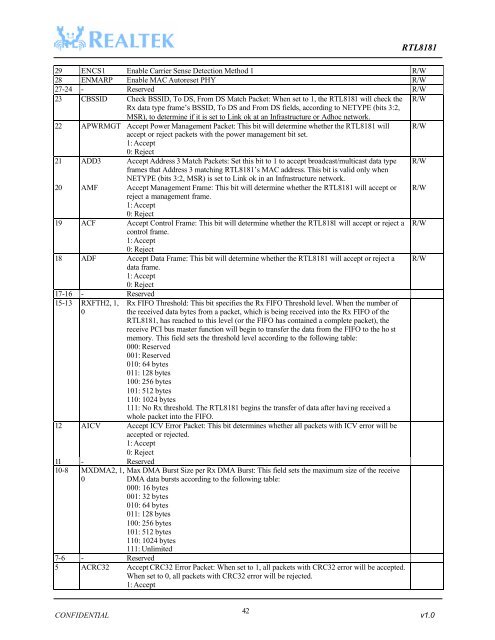

<strong>RTL8181</strong>29 ENCS1 Enable Carrier Sense Detection Method 1 R/W28 ENMARP Enable MAC Autoreset PHY R/W27-24 - Reserved R/W23 CBSSID Check BSSID, To DS, From DS Match Packet: When set to 1, the <strong>RTL8181</strong> will check the R/WRx data type frame’s BSSID, To DS and From DS fields, according to NETYPE (bits 3:2,MSR), to determine if it is set to Link ok at an Infrastructure or Adhoc network.22 APWRMGT Accept Power Management Packet: This bit will determine whether the <strong>RTL8181</strong> will R/Waccept or reject packets with the power management bit set.1: Accept0: Reject21 ADD3 Accept Address 3 Match Packets: Set this bit to 1 to accept broadcast/multicast data type R/Wframes that Address 3 matching <strong>RTL8181</strong>’s MAC address. This bit is valid only whenNETYPE (bits 3:2, MSR) is set to Link ok in an Infrastructure network.20 AMF Accept Management Frame: This bit will determine whether the <strong>RTL8181</strong> will accept or R/Wreject a management frame.1: Accept0: Reject19 ACF Accept Control Frame: This bit will determine whether the <strong>RTL8181</strong> will accept or reject a R/Wcontrol frame.1: Accept0: Reject18 ADF Accept Data Frame: This bit will determine whether the <strong>RTL8181</strong> will accept or reject adata frame.1: Accept0: RejectR/W17-16 - Reserved15-13 RXFTH2, 1,0Rx FIFO Threshold: This bit specifies the Rx FIFO Threshold level. When the number ofthe received data bytes from a packet, which is being received into the Rx FIFO of the<strong>RTL8181</strong>, has reached to this level (or the FIFO has contained a complete packet), thereceive PCI bus master function will begin to transfer the data from the FIFO to the ho stmemory. This field sets the threshold level according to the following table:000: Reserved001: Reserved010: 64 bytes011: 128 bytes100: 256 bytes101: 512 bytes110: 1024 bytes111: No Rx threshold. The <strong>RTL8181</strong> begins the transfer of data after having received awhole packet into the FIFO.12 AICV Accept ICV Error Packet: This bit determines whether all packets with ICV error will beaccepted or rejected.1: Accept0: Reject11 - Reserved10-8 MXDMA2, 1,0Max DMA Burst Size per Rx DMA Burst: This field sets the maximum size of the receiveDMA data bursts according to the following table:000: 16 bytes001: 32 bytes010: 64 bytes011: 128 bytes100: 256 bytes101: 512 bytes110: 1024 bytes111: Unlimited7-6 - Reserved5 ACRC32 Accept CRC32 Error Packet: When set to 1, all packets with CRC32 error will be accepted.When set to 0, all packets with CRC32 error will be rejected.1: Accept42CONFIDENTIAL v1.0