RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

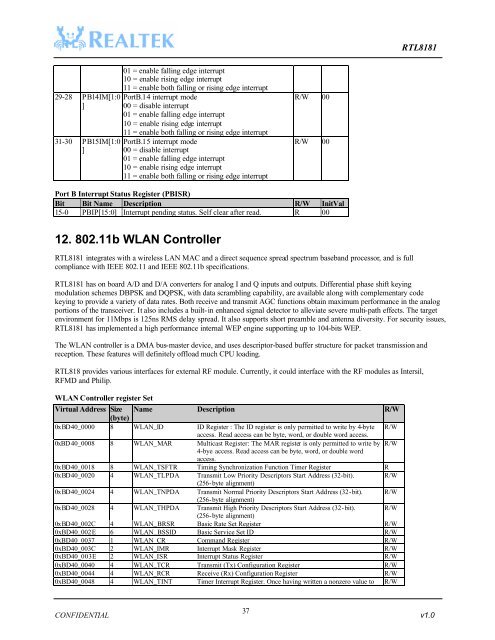

<strong>RTL8181</strong>29-28 PB14IM[1:0]31-30 PB15IM[1:0]01 = enable falling edge interrupt10 = enable rising edge interrupt11 = enable both falling or rising edge interruptPortB.14 interrupt mode00 = disable interrupt01 = enable falling edge interrupt10 = enable rising edge interrupt11 = enable both falling or rising edge interruptPortB.15 interrupt mode00 = disable interrupt01 = enable falling edge interrupt10 = enable rising edge interrupt11 = enable both falling or rising edge interruptR/W 00R/W 00Port B Interrupt Status Register (PBISR)Bit Bit Name Description R/W InitVal15-0 PBIP[15:0] Interrupt pending status. Self clear after read. R 0012. 802.11b W<strong>LAN</strong> <strong>Controller</strong><strong>RTL8181</strong> integrates with a wireless <strong>LAN</strong> MAC and a direct sequence spread spectrum baseband processor, and is fullcompliance with IEEE 802.11 and IEEE 802.11b specifications.<strong>RTL8181</strong> has on board A/D and D/A converters for analog I and Q inputs and outputs. Differential phase shift keyingmodulation schemes DBPSK and DQPSK, with data scrambling capability, are available along with complementary codekeying to provide a variety of data rates. Both receive and transmit AGC functions obtain maximum performance in the analogportions of the transceiver. It also includes a built-in enhanced signal detector to alleviate severe multi-path effects. The targetenvironment for 11Mbps is 125ns RMS delay spread. It also supports short preamble and antenna diversity. For security issues,<strong>RTL8181</strong> has implemented a high performance internal WEP engine supporting up to 104-bits WEP.The W<strong>LAN</strong> controller is a DMA bus-master device, and uses descriptor-based buffer structure for packet transmission andreception. These features will definitely offload much CPU loading.RTL818 provides various interfaces for external RF module. Currently, it could interface with the RF modules as Intersil,RFMD and Philip.W<strong>LAN</strong> <strong>Controller</strong> register SetVirtual Address Size Name Description R/W(byte)0xBD40_0000 8 W<strong>LAN</strong>_ID ID Register : The ID register is only permitted to write by 4-byte R/Waccess. Read access can be byte, word, or double word access.0xBD40_0008 8 W<strong>LAN</strong>_MAR Multicast Register: The MAR register is only permitted to write by R/W4-bye access. Read access can be byte, word, or double wordaccess.0xBD40_0018 8 W<strong>LAN</strong>_TSFTR Timing Synchronization Function Timer Register R0xBD40_0020 4 W<strong>LAN</strong>_TLPDA Transmit Low Priority Descriptors Start Address (32-bit). R/W(256-byte alignment)0xBD40_0024 4 W<strong>LAN</strong>_TNPDA Transmit Normal Priority Descriptors Start Address (32-bit). R/W(256-byte alignment)0xBD40_0028 4 W<strong>LAN</strong>_THPDA Transmit High Priority Descriptors Start Address (32-bit). R/W(256-byte alignment)0xBD40_002C 4 W<strong>LAN</strong>_BRSR Basic Rate Set Register R/W0xBD40_002E 6 W<strong>LAN</strong>_BSSID Basic Service Set ID R/W0xBD40_0037 1 W<strong>LAN</strong>_CR Command Register R/W0xBD40_003C 2 W<strong>LAN</strong>_IMR Interrupt Mask Register R/W0xBD40_003E 2 W<strong>LAN</strong>_ISR Interrupt Status Register R/W0xBD40_0040 4 W<strong>LAN</strong>_TCR Transmit (Tx) Configuration Register R/W0xBD40_0044 4 W<strong>LAN</strong>_RCR Receive (Rx) Configuration Register R/W0xBD40_0048 4 W<strong>LAN</strong>_TINT Timer Interrupt Register. Once having written a nonzero value to R/W37CONFIDENTIAL v1.0