RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

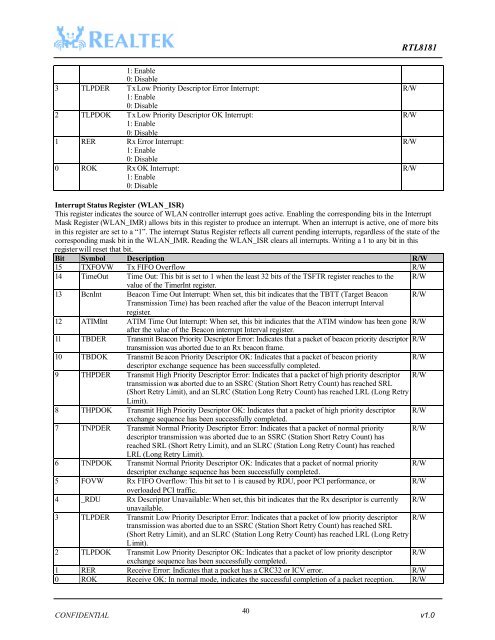

<strong>RTL8181</strong>1: Enable0: Disable3 TLPDER Tx Low Priority Descriptor Error Interrupt:1: Enable0: Disable2 TLPDOK Tx Low Priority Descriptor OK Interrupt:1: Enable0: Disable1 RER Rx Error Interrupt:1: Enable0: Disable0 ROK Rx OK Interrupt:1: Enable0: DisableR/WR/WR/WR/WInterrupt Status Register (W<strong>LAN</strong>_ISR)This register indicates the source of W<strong>LAN</strong> controller interrupt goes active. Enabling the corresponding bits in the InterruptMask Register (W<strong>LAN</strong>_IMR) allows bits in this register to produce an interrupt. When an interrupt is active, one of more bitsin this register are set to a “1”. The interrupt Status Register reflects all current pending interrupts, regardless of the state of thecorresponding mask bit in the W<strong>LAN</strong>_IMR. Reading the W<strong>LAN</strong>_ISR clears all interrupts. Writing a 1 to any bit in thisregister will reset that bit.Bit Symbol Description R/W15 TXFOVW Tx FIFO Overflow R/W14 TimeOut Time Out: This bit is set to 1 when the least 32 bits of the TSFTR register reaches to the R/Wvalue of the TimerInt register.13 BcnInt Beacon Time Out Interrupt: When set, this bit indicates that the TBTT (Target Beacon R/WTransmission Time) has been reached after the value of the Beacon interrupt Intervalregister.12 ATIMInt ATIM Time Out Interrupt: When set, this bit indicates that the ATIM window has been gone R/Wafter the value of the Beacon interrupt Interval register.11 TBDER Transmit Beacon Priority Descriptor Error: Indicates that a packet of beacon priority descriptor R/Wtransmission was aborted due to an Rx beacon frame.10 TBDOK Transmit Beacon Priority Descriptor OK: Indicates that a packet of beacon priority R/Wdescriptor exchange sequence has been successfully completed.9 THPDER Transmit High Priority Descriptor Error: Indicates that a packet of high priority descriptor R/Wtransmission was aborted due to an SSRC (Station Short Retry Count) has reached SRL(Short Retry Limit), and an SLRC (Station Long Retry Count) has reached LRL (Long RetryLimit).8 THPDOK Transmit High Priority Descriptor OK: Indicates that a packet of high priority descriptor R/Wexchange sequence has been successfully completed.7 TNPDER Transmit Normal Priority Descriptor Error: Indicates that a packet of normal priority R/Wdescriptor transmission was aborted due to an SSRC (Station Short Retry Count) hasreached SRL (Short Retry Limit), and an SLRC (Station Long Retry Count) has reachedLRL (Long Retry Limit).6 TNPDOK Transmit Normal Priority Descriptor OK: Indicates that a packet of normal priority R/Wdescriptor exchange sequence has been successfully completed.5 FOVW Rx FIFO Overflow: This bit set to 1 is caused by RDU, poor PCI performance, or R/Woverloaded PCI traffic.4 _RDU Rx Descriptor Unavailable: When set, this bit indicates that the Rx descriptor is currently R/Wunavailable.3 TLPDER Transmit Low Priority Descriptor Error: Indicates that a packet of low priority descriptor R/Wtransmission was aborted due to an SSRC (Station Short Retry Count) has reached SRL(Short Retry Limit), and an SLRC (Station Long Retry Count) has reached LRL (Long RetryLimit).2 TLPDOK Transmit Low Priority Descriptor OK: Indicates that a packet of low priority descriptor R/Wexchange sequence has been successfully completed.1 RER Receive Error: Indicates that a packet has a CRC32 or ICV error. R/W0 ROK Receive OK: In normal mode, indicates the successful completion of a packet reception. R/W40CONFIDENTIAL v1.0