RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

RTL8181 Wireless LAN Access Point/Gateway Controller DATA ...

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

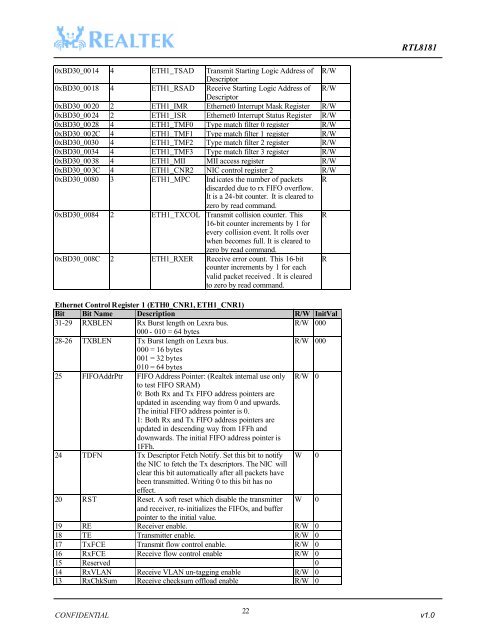

<strong>RTL8181</strong>0xBD30_0014 4 ETH1_TSAD Transmit Starting Logic Address of R/WDescriptor0xBD30_0018 4 ETH1_RSAD Receive Starting Logic Address of R/WDescriptor0xBD30_0020 2 ETH1_IMR Ethernet0 Interrupt Mask Register R/W0xBD30_0024 2 ETH1_ISR Ethernet0 Interrupt Status Register R/W0xBD30_0028 4 ETH1_TMF0 Type match filter 0 register R/W0xBD30_002C 4 ETH1_TMF1 Type match filter 1 register R/W0xBD30_0030 4 ETH1_TMF2 Type match filter 2 register R/W0xBD30_0034 4 ETH1_TMF3 Type match filter 3 register R/W0xBD30_0038 4 ETH1_MII MII access register R/W0xBD30_003C 4 ETH1_CNR2 NIC control register 2 R/W0xBD30_0080 3 ETH1_MPC Ind icates the number of packets Rdiscarded due to rx FIFO overflow.It is a 24-bit counter. It is cleared tozero by read command.0xBD30_0084 2 ETH1_TXCOL Transmit collision counter. This R16-bit counter increments by 1 forevery collision event. It rolls overwhen becomes full. It is cleared tozero by read command.0xBD30_008C 2 ETH1_RXER Receive error count. This 16-bitcounter increments by 1 for eachvalid packet received . It is clearedto zero by read command.REthernet Control Register 1 (ETH0_CNR1, ETH1_CNR1)Bit Bit Name Description R/W InitVal31-29 RXBLEN Rx Burst length on Lexra bus.R/W 000000 - 010 = 64 bytes28-26 TXBLEN Tx Burst length on Lexra bus.R/W 000000 = 16 bytes001 = 32 bytes010 = 64 bytes25 FIFOAddrPtr FIFO Address <strong>Point</strong>er: (Realtek internal use only R/W 0to test FIFO SRAM)0: Both Rx and Tx FIFO address pointers areupdated in ascending way from 0 and upwards.The initial FIFO address pointer is 0.1: Both Rx and Tx FIFO address pointers areupdated in descending way from 1FFh anddownwards. The initial FIFO address pointer is1FFh.24 TDFN Tx Descriptor Fetch Notify. Set this bit to notify W 0the NIC to fetch the Tx descriptors. The NIC willclear this bit automatically after all packets havebeen transmitted. Writing 0 to this bit has noeffect.20 RST Reset. A soft reset which disable the transmitter W 0and receiver, re-initializes the FIFOs, and bufferpointer to the initial value.19 RE Receiver enable. R/W 018 TE Transmitter enable. R/W 017 TxFCE Transmit flow control enable. R/W 016 RxFCE Receive flow control enable R/W 015 Reserved 014 RxV<strong>LAN</strong> Receive V<strong>LAN</strong> un-tagging enable R/W 013 RxChkSum Receive checksum offload enable R/W 022CONFIDENTIAL v1.0