Architecture Modeling - SPES 2020

Architecture Modeling - SPES 2020

Architecture Modeling - SPES 2020

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>Architecture</strong> <strong>Modeling</strong><br />

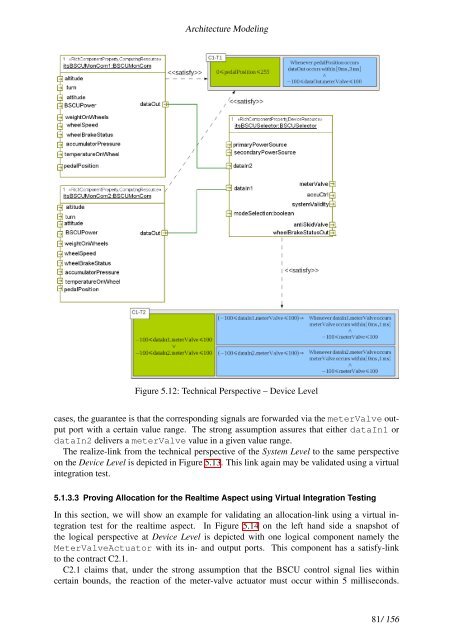

Figure 5.12: Technical Perspective – Device Level<br />

cases, the guarantee is that the corresponding signals are forwarded via the meterValve output<br />

port with a certain value range. The strong assumption assures that either dataIn1 or<br />

dataIn2 delivers a meterValve value in a given value range.<br />

The realize-link from the technical perspective of the System Level to the same perspective<br />

on the Device Level is depicted in Figure 5.13. This link again may be validated using a virtual<br />

integration test.<br />

5.1.3.3 Proving Allocation for the Realtime Aspect using Virtual Integration Testing<br />

In this section, we will show an example for validating an allocation-link using a virtual integration<br />

test for the realtime aspect. In Figure 5.14 on the left hand side a snapshot of<br />

the logical perspective at Device Level is depicted with one logical component namely the<br />

MeterValveActuator with its in- and output ports. This component has a satisfy-link<br />

to the contract C2.1.<br />

C2.1 claims that, under the strong assumption that the BSCU control signal lies within<br />

certain bounds, the reaction of the meter-valve actuator must occur within 5 milliseconds.<br />

81/ 156