Hardware Manual - RTD Embedded Technologies, Inc.

Hardware Manual - RTD Embedded Technologies, Inc.

Hardware Manual - RTD Embedded Technologies, Inc.

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

38 DM6425HR dataModule BDM-610010034 Rev C<br />

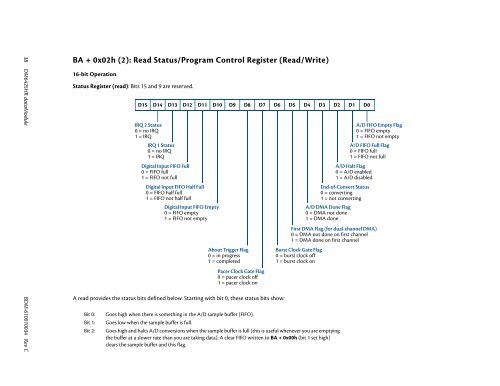

BA + 0x02h (2): Read Status/Program Control Register (Read/Write)<br />

16-bit Operation.<br />

Status Register (read): Bits 15 and 9 are reserved.<br />

A read provides the status bits defined below. Starting with bit 0, these status bits show:<br />

Bit 0:<br />

Bit 1:<br />

Bit 2:<br />

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0<br />

IRQ 2 Status<br />

0 = no IRQ<br />

1 = IRQ<br />

IRQ 1 Status<br />

0 = no IRQ<br />

1 = IRQ<br />

Digital Input FIFO Full<br />

0 = FIFO full<br />

1 = FIFO not full<br />

Digital Input FIFO Half Full<br />

0 = FIFO half full<br />

1 = FIFO not half full<br />

Digital Input FIFO Empty<br />

0 = FIFO empty<br />

1 = FIFO not empty<br />

About Trigger Flag<br />

0 = in progress<br />

1 = completed<br />

Pacer Clock Gate Flag<br />

0 = pacer clock off<br />

1 = pacer clock on<br />

Goes high when there is something in the A/D sample buffer (FIFO).<br />

Goes low when the sample buffer is full.<br />

Goes high and halts A/D conversions when the sample buffer is full (this is useful whenever you are emptying<br />

the buffer at a slower rate than you are taking data). A clear FIFO written to BA + 0x00h (bit 1 set high)<br />

clears the sample buffer and this flag.<br />

A/D FIFO Full Flag<br />

0 = FIFO full<br />

1 = FIFO not full<br />

A/D Halt Flag<br />

0 = A/D enabled<br />

1 = A/D disabled<br />

First DMA Flag (for dual-channel DMA)<br />

0 = DMA not done on first channel<br />

1 = DMA done on first channel<br />

Burst Clock Gate Flag<br />

0 = burst clock off<br />

1 = burst clock on<br />

End-of-Convert Status<br />

0 = converting<br />

1 = not converting<br />

A/D DMA Done Flag<br />

0 = DMA not done<br />

1 = DMA done<br />

A/D FIFO Empty Flag<br />

0 = FIFO empty<br />

1 = FIFO not empty