Text anzeigen (PDF) - bei DuEPublico

Text anzeigen (PDF) - bei DuEPublico

Text anzeigen (PDF) - bei DuEPublico

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

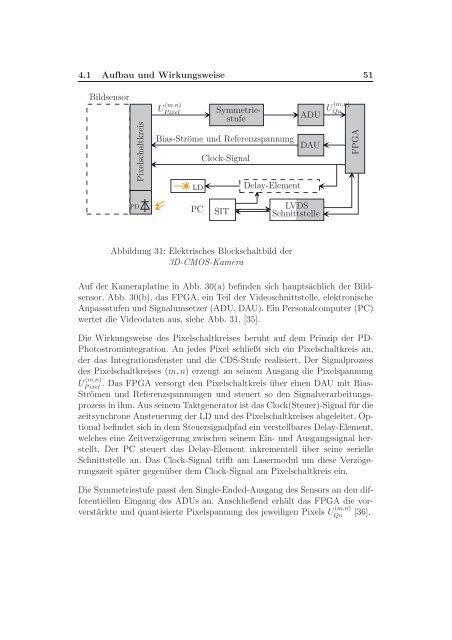

4.1 Aufbau und Wirkungsweise 51<br />

Bildsensor<br />

Pixelschaltkreis<br />

PD<br />

U (m,n)<br />

Pixel<br />

Bias-Ströme und Referenzspannung<br />

LD<br />

Symmetriestufe<br />

Clock-Signal<br />

PC SIT<br />

Delay-Element<br />

Abbildung 31: Elektrisches Blockschaltbild der<br />

3D-CMOS-Kamera<br />

ADU<br />

DAU<br />

LVDS<br />

Schnittstelle<br />

U (m,n)<br />

Qu<br />

Auf der Kameraplatine in Abb. 30(a) befinden sich hauptsächlich der Bildsensor,<br />

Abb. 30(b), das FPGA, ein Teil der Videoschnittstelle, elektronische<br />

Anpassstufen und Signalumsetzer (ADU, DAU). Ein Personalcomputer (PC)<br />

wertet die Videodaten aus, siehe Abb. 31, [35].<br />

Die Wirkungsweise des Pixelschaltkreises beruht auf dem Prinzip der PD-<br />

Photostromintegration. An jedes Pixel schließt sich ein Pixelschaltkreis an,<br />

der das Integrationsfenster und die CDS-Stufe realisiert. Der Signalprozess<br />

des Pixelschaltkreises (m, n) erzeugt an seinem Ausgang die Pixelspannung<br />

U (m,n)<br />

Pixel . Das FPGA versorgt den Pixelschaltkreis über einen DAU mit Bias-<br />

Strömen und Referenzspannungen und steuert so den Signalverar<strong>bei</strong>tungsprozess<br />

in ihm. Aus seinem Taktgenerator ist das Clock(Steuer)-Signal für die<br />

zeitsynchrone Ansteuerung der LD und des Pixelschaltkreises abgeleitet. Optional<br />

befindet sich in dem Steuersignalpfad ein verstellbares Delay-Element,<br />

welches eine Zeitverzögerung zwischen seinem Ein- und Ausgangssignal herstellt.<br />

Der PC steuert das Delay-Element inkrementell über seine serielle<br />

Schnittstelle an. Das Clock-Signal trifft am Lasermodul um diese Verzögerungszeit<br />

später gegenüber dem Clock-Signal am Pixelschaltkreis ein.<br />

Die Symmetriestufe passt den Single-Ended-Ausgang des Sensors an den differentiellen<br />

Eingang des ADUs an. Anschließend erhält das FPGA die vorverstärkte<br />

und quantisierte Pixelspannung des jeweiligen Pixels U (m,n)<br />

Qu [36].<br />

FPGA