J-Link / J-Trace User Guide (UM08001) - Microcontrollers

J-Link / J-Trace User Guide (UM08001) - Microcontrollers

J-Link / J-Trace User Guide (UM08001) - Microcontrollers

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

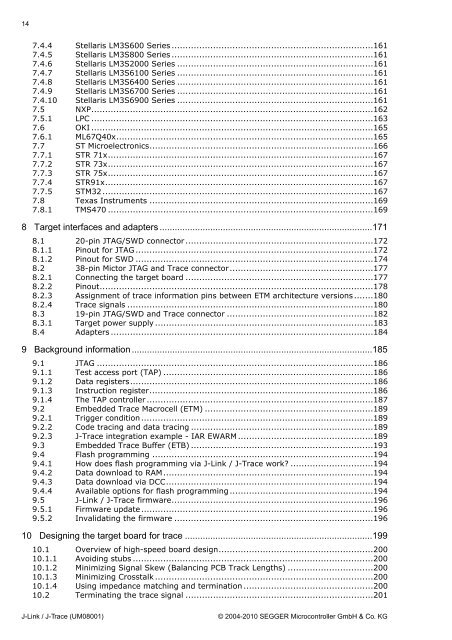

14<br />

7.4.4 Stellaris LM3S600 Series .........................................................................161<br />

7.4.5 Stellaris LM3S800 Series .........................................................................161<br />

7.4.6 Stellaris LM3S2000 Series .......................................................................161<br />

7.4.7 Stellaris LM3S6100 Series .......................................................................161<br />

7.4.8 Stellaris LM3S6400 Series .......................................................................161<br />

7.4.9 Stellaris LM3S6700 Series .......................................................................161<br />

7.4.10 Stellaris LM3S6900 Series .......................................................................161<br />

7.5 NXP......................................................................................................162<br />

7.5.1 LPC ......................................................................................................163<br />

7.6 OKI ......................................................................................................165<br />

7.6.1 ML67Q40x.............................................................................................165<br />

7.7 ST Microelectronics.................................................................................166<br />

7.7.1 STR 71x................................................................................................167<br />

7.7.2 STR 73x................................................................................................167<br />

7.7.3 STR 75x................................................................................................167<br />

7.7.4 STR91x.................................................................................................167<br />

7.7.5 STM32 ..................................................................................................167<br />

7.8 Texas Instruments .................................................................................169<br />

7.8.1 TMS470 ................................................................................................169<br />

8 Target interfaces and adapters ....................................................................................171<br />

8.1 20-pin JTAG/SWD connector ....................................................................172<br />

8.1.1 Pinout for JTAG ......................................................................................172<br />

8.1.2 Pinout for SWD ......................................................................................174<br />

8.2 38-pin Mictor JTAG and <strong>Trace</strong> connector....................................................177<br />

8.2.1 Connecting the target board ....................................................................177<br />

8.2.2 Pinout...................................................................................................178<br />

8.2.3 Assignment of trace information pins between ETM architecture versions .......180<br />

8.2.4 <strong>Trace</strong> signals .........................................................................................180<br />

8.3 19-pin JTAG/SWD and <strong>Trace</strong> connector .....................................................182<br />

8.3.1 Target power supply ...............................................................................183<br />

8.4 Adapters ...............................................................................................184<br />

9 Background information ...............................................................................................185<br />

9.1 JTAG ....................................................................................................186<br />

9.1.1 Test access port (TAP) ............................................................................186<br />

9.1.2 Data registers........................................................................................186<br />

9.1.3 Instruction register.................................................................................186<br />

9.1.4 The TAP controller ..................................................................................187<br />

9.2 Embedded <strong>Trace</strong> Macrocell (ETM) .............................................................189<br />

9.2.1 Trigger condition ....................................................................................189<br />

9.2.2 Code tracing and data tracing ..................................................................189<br />

9.2.3 J-<strong>Trace</strong> integration example - IAR EWARM .................................................189<br />

9.3 Embedded <strong>Trace</strong> Buffer (ETB) ..................................................................193<br />

9.4 Flash programming ................................................................................194<br />

9.4.1 How does flash programming via J-<strong>Link</strong> / J-<strong>Trace</strong> work? ..............................194<br />

9.4.2 Data download to RAM............................................................................194<br />

9.4.3 Data download via DCC...........................................................................194<br />

9.4.4 Available options for flash programming ....................................................194<br />

9.5 J-<strong>Link</strong> / J-<strong>Trace</strong> firmware.........................................................................196<br />

9.5.1 Firmware update....................................................................................196<br />

9.5.2 Invalidating the firmware ........................................................................196<br />

10 Designing the target board for trace ..........................................................................199<br />

10.1 Overview of high-speed board design........................................................200<br />

10.1.1 Avoiding stubs .......................................................................................200<br />

10.1.2 Minimizing Signal Skew (Balancing PCB Track Lengths) ...............................200<br />

10.1.3 Minimizing Crosstalk ...............................................................................200<br />

10.1.4 Using impedance matching and termination ...............................................200<br />

10.2 Terminating the trace signal ....................................................................201<br />

J-<strong>Link</strong> / J-<strong>Trace</strong> (<strong>UM08001</strong>) © 2004-2010 SEGGER Microcontroller GmbH & Co. KG