J-Link / J-Trace User Guide (UM08001) - Microcontrollers

J-Link / J-Trace User Guide (UM08001) - Microcontrollers

J-Link / J-Trace User Guide (UM08001) - Microcontrollers

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

180 CHAPTER 8 Target interfaces and adapters<br />

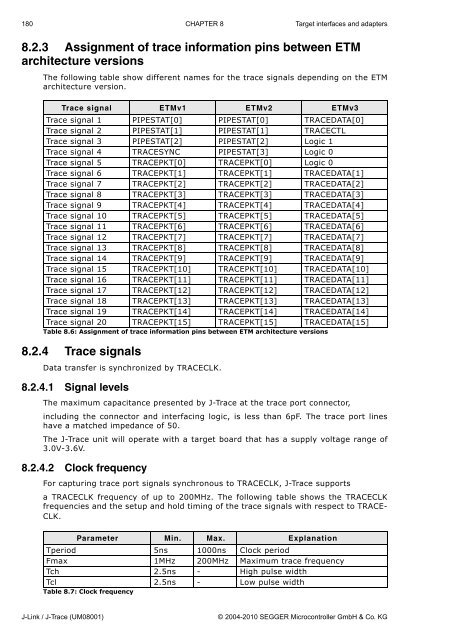

8.2.3 Assignment of trace information pins between ETM<br />

architecture versions<br />

The following table show different names for the trace signals depending on the ETM<br />

architecture version.<br />

<strong>Trace</strong> signal ETMv1 ETMv2 ETMv3<br />

<strong>Trace</strong> signal 1 PIPESTAT[0] PIPESTAT[0] TRACEDATA[0]<br />

<strong>Trace</strong> signal 2 PIPESTAT[1] PIPESTAT[1] TRACECTL<br />

<strong>Trace</strong> signal 3 PIPESTAT[2] PIPESTAT[2] Logic 1<br />

<strong>Trace</strong> signal 4 TRACESYNC PIPESTAT[3] Logic 0<br />

<strong>Trace</strong> signal 5 TRACEPKT[0] TRACEPKT[0] Logic 0<br />

<strong>Trace</strong> signal 6 TRACEPKT[1] TRACEPKT[1] TRACEDATA[1]<br />

<strong>Trace</strong> signal 7 TRACEPKT[2] TRACEPKT[2] TRACEDATA[2]<br />

<strong>Trace</strong> signal 8 TRACEPKT[3] TRACEPKT[3] TRACEDATA[3]<br />

<strong>Trace</strong> signal 9 TRACEPKT[4] TRACEPKT[4] TRACEDATA[4]<br />

<strong>Trace</strong> signal 10 TRACEPKT[5] TRACEPKT[5] TRACEDATA[5]<br />

<strong>Trace</strong> signal 11 TRACEPKT[6] TRACEPKT[6] TRACEDATA[6]<br />

<strong>Trace</strong> signal 12 TRACEPKT[7] TRACEPKT[7] TRACEDATA[7]<br />

<strong>Trace</strong> signal 13 TRACEPKT[8] TRACEPKT[8] TRACEDATA[8]<br />

<strong>Trace</strong> signal 14 TRACEPKT[9] TRACEPKT[9] TRACEDATA[9]<br />

<strong>Trace</strong> signal 15 TRACEPKT[10] TRACEPKT[10] TRACEDATA[10]<br />

<strong>Trace</strong> signal 16 TRACEPKT[11] TRACEPKT[11] TRACEDATA[11]<br />

<strong>Trace</strong> signal 17 TRACEPKT[12] TRACEPKT[12] TRACEDATA[12]<br />

<strong>Trace</strong> signal 18 TRACEPKT[13] TRACEPKT[13] TRACEDATA[13]<br />

<strong>Trace</strong> signal 19 TRACEPKT[14] TRACEPKT[14] TRACEDATA[14]<br />

<strong>Trace</strong> signal 20 TRACEPKT[15] TRACEPKT[15] TRACEDATA[15]<br />

Table 8.6: Assignment of trace information pins between ETM architecture versions<br />

8.2.4 <strong>Trace</strong> signals<br />

Data transfer is synchronized by TRACECLK.<br />

8.2.4.1 Signal levels<br />

The maximum capacitance presented by J-<strong>Trace</strong> at the trace port connector,<br />

including the connector and interfacing logic, is less than 6pF. The trace port lines<br />

have a matched impedance of 50.<br />

The J-<strong>Trace</strong> unit will operate with a target board that has a supply voltage range of<br />

3.0V-3.6V.<br />

8.2.4.2 Clock frequency<br />

For capturing trace port signals synchronous to TRACECLK, J-<strong>Trace</strong> supports<br />

a TRACECLK frequency of up to 200MHz. The following table shows the TRACECLK<br />

frequencies and the setup and hold timing of the trace signals with respect to TRACE-<br />

CLK.<br />

Parameter Min. Max. Explanation<br />

Tperiod 5ns 1000ns Clock period<br />

Fmax 1MHz 200MHz Maximum trace frequency<br />

Tch 2.5ns - High pulse width<br />

Tcl<br />

Table 8.7: Clock frequency<br />

2.5ns - Low pulse width<br />

J-<strong>Link</strong> / J-<strong>Trace</strong> (<strong>UM08001</strong>) © 2004-2010 SEGGER Microcontroller GmbH & Co. KG