Parallel Flash Loader Megafunction User Guide (PDF) - Altera

Parallel Flash Loader Megafunction User Guide (PDF) - Altera

Parallel Flash Loader Megafunction User Guide (PDF) - Altera

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Page 10<br />

Functional Description<br />

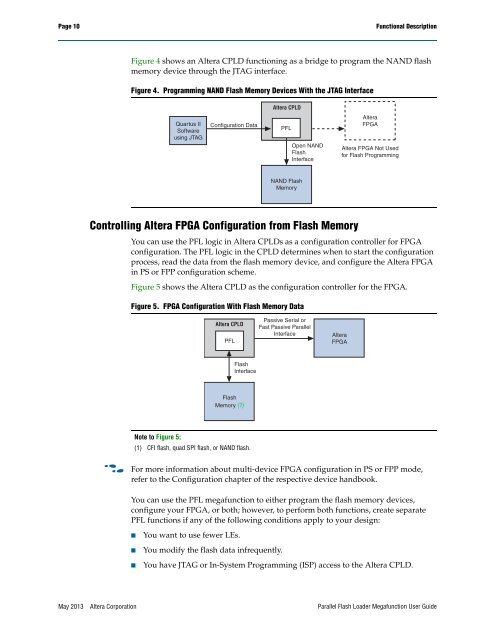

Figure 4 shows an <strong>Altera</strong> CPLD functioning as a bridge to program the NAND flash<br />

memory device through the JTAG interface.<br />

Figure 4. Programming NAND <strong>Flash</strong> Memory Devices With the JTAG Interface<br />

<strong>Altera</strong> CPLD<br />

Quartus II<br />

Software<br />

using JTAG<br />

Configuration Data<br />

PFL<br />

Open NAND<br />

<strong>Flash</strong><br />

Interface<br />

<strong>Altera</strong><br />

FPGA<br />

<strong>Altera</strong> FPGA Not Used<br />

for <strong>Flash</strong> Programming<br />

NAND <strong>Flash</strong><br />

Memory<br />

Controlling <strong>Altera</strong> FPGA Configuration from <strong>Flash</strong> Memory<br />

You can use the PFL logic in <strong>Altera</strong> CPLDs as a configuration controller for FPGA<br />

configuration. The PFL logic in the CPLD determines when to start the configuration<br />

process, read the data from the flash memory device, and configure the <strong>Altera</strong> FPGA<br />

in PS or FPP configuration scheme.<br />

Figure 5 shows the <strong>Altera</strong> CPLD as the configuration controller for the FPGA.<br />

Figure 5. FPGA Configuration With <strong>Flash</strong> Memory Data<br />

<strong>Altera</strong> CPLD<br />

PFL<br />

Passive Serial or<br />

Fast Passive <strong>Parallel</strong><br />

Interface<br />

<strong>Altera</strong><br />

FPGA<br />

<strong>Flash</strong><br />

Interface<br />

<strong>Flash</strong><br />

Memory (1)<br />

Note to Figure 5:<br />

(1) CFI flash, quad SPI flash, or NAND flash.<br />

f<br />

For more information about multi-device FPGA configuration in PS or FPP mode,<br />

refer to the Configuration chapter of the respective device handbook.<br />

You can use the PFL megafunction to either program the flash memory devices,<br />

configure your FPGA, or both; however, to perform both functions, create separate<br />

PFL functions if any of the following conditions apply to your design:<br />

■<br />

■<br />

■<br />

You want to use fewer LEs.<br />

You modify the flash data infrequently.<br />

You have JTAG or In-System Programming (ISP) access to the <strong>Altera</strong> CPLD.<br />

May 2013 <strong>Altera</strong> Corporation <strong>Parallel</strong> <strong>Flash</strong> <strong>Loader</strong> <strong>Megafunction</strong> <strong>User</strong> <strong>Guide</strong>