Parallel Flash Loader Megafunction User Guide (PDF) - Altera

Parallel Flash Loader Megafunction User Guide (PDF) - Altera

Parallel Flash Loader Megafunction User Guide (PDF) - Altera

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Using the PFL <strong>Megafunction</strong> Page 27<br />

Table 7. PFL Timing Constraints<br />

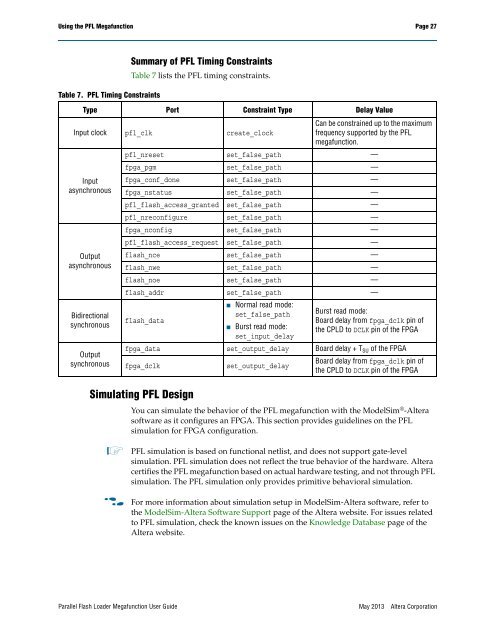

Summary of PFL Timing Constraints<br />

Table 7 lists the PFL timing constraints.<br />

Type Port Constraint Type Delay Value<br />

Can be constrained up to the maximum<br />

Input clock pfl_clk create_clock<br />

frequency supported by the PFL<br />

megafunction.<br />

pfl_nreset set_false_path —<br />

fpga_pgm set_false_path —<br />

Input fpga_conf_done set_false_path —<br />

asynchronous fpga_nstatus set_false_path —<br />

pfl_flash_access_granted set_false_path —<br />

pfl_nreconfigure set_false_path —<br />

fpga_nconfig set_false_path —<br />

pfl_flash_access_request set_false_path —<br />

Output flash_nce set_false_path —<br />

asynchronous flash_nwe set_false_path —<br />

flash_noe set_false_path —<br />

flash_addr set_false_path —<br />

Bidirectional<br />

synchronous<br />

Output<br />

synchronous<br />

flash_data<br />

Simulating PFL Design<br />

■<br />

■<br />

Normal read mode:<br />

set_false_path<br />

Burst read mode:<br />

set_input_delay<br />

Burst read mode:<br />

Board delay from fpga_dclk pin of<br />

the CPLD to DCLK pin of the FPGA<br />

fpga_data set_output_delay Board delay + T SU of the FPGA<br />

fpga_dclk<br />

set_output_delay<br />

Board delay from fpga_dclk pin of<br />

the CPLD to DCLK pin of the FPGA<br />

You can simulate the behavior of the PFL megafunction with the ModelSim ® -<strong>Altera</strong><br />

software as it configures an FPGA. This section provides guidelines on the PFL<br />

simulation for FPGA configuration.<br />

1 PFL simulation is based on functional netlist, and does not support gate-level<br />

simulation. PFL simulation does not reflect the true behavior of the hardware. <strong>Altera</strong><br />

certifies the PFL megafunction based on actual hardware testing, and not through PFL<br />

simulation. The PFL simulation only provides primitive behavioral simulation.<br />

f<br />

For more information about simulation setup in ModelSim-<strong>Altera</strong> software, refer to<br />

the ModelSim-<strong>Altera</strong> Software Support page of the <strong>Altera</strong> website. For issues related<br />

to PFL simulation, check the known issues on the Knowledge Database page of the<br />

<strong>Altera</strong> website.<br />

<strong>Parallel</strong> <strong>Flash</strong> <strong>Loader</strong> <strong>Megafunction</strong> <strong>User</strong> <strong>Guide</strong><br />

May 2013<br />

<strong>Altera</strong> Corporation