Parallel Flash Loader Megafunction User Guide (PDF) - Altera

Parallel Flash Loader Megafunction User Guide (PDF) - Altera

Parallel Flash Loader Megafunction User Guide (PDF) - Altera

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Page 50<br />

Specifications<br />

■<br />

■<br />

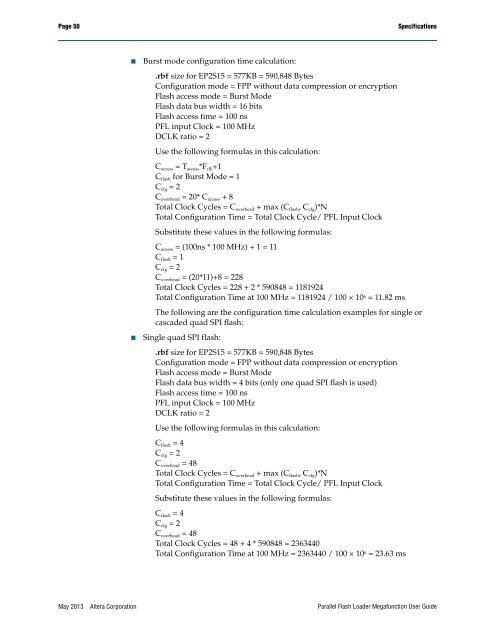

Burst mode configuration time calculation:<br />

.rbf size for EP2S15 = 577KB = 590,848 Bytes<br />

Configuration mode = FPP without data compression or encryption<br />

<strong>Flash</strong> access mode = Burst Mode<br />

<strong>Flash</strong> data bus width = 16 bits<br />

<strong>Flash</strong> access time = 100 ns<br />

PFL input Clock = 100 MHz<br />

DCLK ratio = 2<br />

Use the following formulas in this calculation:<br />

C access = T access *F clk +1<br />

C flash for Burst Mode = 1<br />

C cfg = 2<br />

C overhead = 20* C access + 8<br />

Total Clock Cycles = C overhead + max (C flash , C cfg )*N<br />

Total Configuration Time = Total Clock Cycle/ PFL Input Clock<br />

Substitute these values in the following formulas:<br />

C access = (100ns * 100 MHz) + 1 = 11<br />

C flash = 1<br />

C cfg = 2<br />

C overhead = (20*11)+8 = 228<br />

Total Clock Cycles = 228 + 2 * 590848 = 1181924<br />

Total Configuration Time at 100 MHz = 1181924 / 100 × 10 6 = 11.82 ms<br />

The following are the configuration time calculation examples for single or<br />

cascaded quad SPI flash:<br />

Single quad SPI flash:<br />

.rbf size for EP2S15 = 577KB = 590,848 Bytes<br />

Configuration mode = FPP without data compression or encryption<br />

<strong>Flash</strong> access mode = Burst Mode<br />

<strong>Flash</strong> data bus width = 4 bits (only one quad SPI flash is used)<br />

<strong>Flash</strong> access time = 100 ns<br />

PFL input Clock = 100 MHz<br />

DCLK ratio = 2<br />

Use the following formulas in this calculation:<br />

C flash = 4<br />

C cfg = 2<br />

C overhead = 48<br />

Total Clock Cycles = C overhead + max (C flash , C cfg )*N<br />

Total Configuration Time = Total Clock Cycle/ PFL Input Clock<br />

Substitute these values in the following formulas:<br />

C flash = 4<br />

C cfg = 2<br />

C overhead = 48<br />

Total Clock Cycles = 48 + 4 * 590848 = 2363440<br />

Total Configuration Time at 100 MHz = 2363440 / 100 × 10 6 = 23.63 ms<br />

May 2013 <strong>Altera</strong> Corporation <strong>Parallel</strong> <strong>Flash</strong> <strong>Loader</strong> <strong>Megafunction</strong> <strong>User</strong> <strong>Guide</strong>