Parallel Flash Loader Megafunction User Guide (PDF) - Altera

Parallel Flash Loader Megafunction User Guide (PDF) - Altera

Parallel Flash Loader Megafunction User Guide (PDF) - Altera

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

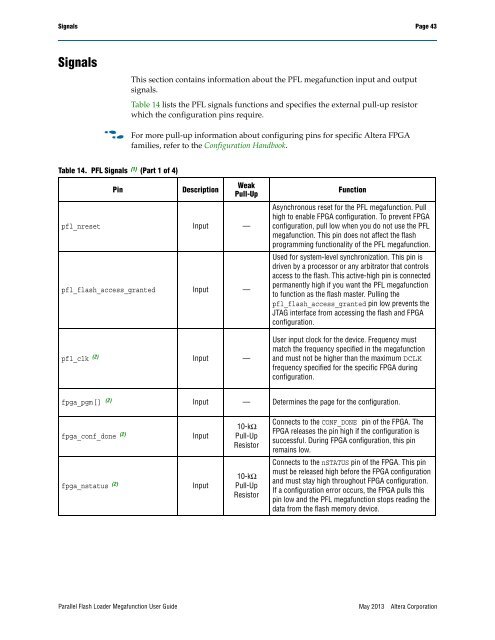

Signals Page 43<br />

Signals<br />

This section contains information about the PFL megafunction input and output<br />

signals.<br />

Table 14 lists the PFL signals functions and specifies the external pull-up resistor<br />

which the configuration pins require.<br />

f<br />

For more pull-up information about configuring pins for specific <strong>Altera</strong> FPGA<br />

families, refer to the Configuration Handbook.<br />

Table 14. PFL Signals (1) (Part 1 of 4)<br />

Pin<br />

Description<br />

Weak<br />

Pull-Up<br />

pfl_nreset Input —<br />

pfl_flash_access_granted Input —<br />

pfl_clk (2) Input —<br />

Function<br />

Asynchronous reset for the PFL megafunction. Pull<br />

high to enable FPGA configuration. To prevent FPGA<br />

configuration, pull low when you do not use the PFL<br />

megafunction. This pin does not affect the flash<br />

programming functionality of the PFL megafunction.<br />

Used for system-level synchronization. This pin is<br />

driven by a processor or any arbitrator that controls<br />

access to the flash. This active-high pin is connected<br />

permanently high if you want the PFL megafunction<br />

to function as the flash master. Pulling the<br />

pfl_flash_access_granted pin low prevents the<br />

JTAG interface from accessing the flash and FPGA<br />

configuration.<br />

<strong>User</strong> input clock for the device. Frequency must<br />

match the frequency specified in the megafunction<br />

and must not be higher than the maximum DCLK<br />

frequency specified for the specific FPGA during<br />

configuration.<br />

fpga_pgm[] (2) Input — Determines the page for the configuration.<br />

fpga_conf_done (2)<br />

Input<br />

10-kΩ<br />

Pull-Up<br />

Resistor<br />

Connects to the CONF_DONE pin of the FPGA. The<br />

FPGA releases the pin high if the configuration is<br />

successful. During FPGA configuration, this pin<br />

remains low.<br />

Connects to the nSTATUS pin of the FPGA. This pin<br />

must be released high before the FPGA configuration<br />

and must stay high throughout FPGA configuration.<br />

If a configuration error occurs, the FPGA pulls this<br />

pin low and the PFL megafunction stops reading the<br />

data from the flash memory device.<br />

fpga_nstatus (2)<br />

Input<br />

10-kΩ<br />

Pull-Up<br />

Resistor<br />

<strong>Parallel</strong> <strong>Flash</strong> <strong>Loader</strong> <strong>Megafunction</strong> <strong>User</strong> <strong>Guide</strong><br />

May 2013<br />

<strong>Altera</strong> Corporation