Parallel Flash Loader Megafunction User Guide (PDF) - Altera

Parallel Flash Loader Megafunction User Guide (PDF) - Altera

Parallel Flash Loader Megafunction User Guide (PDF) - Altera

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Parameters Page 41<br />

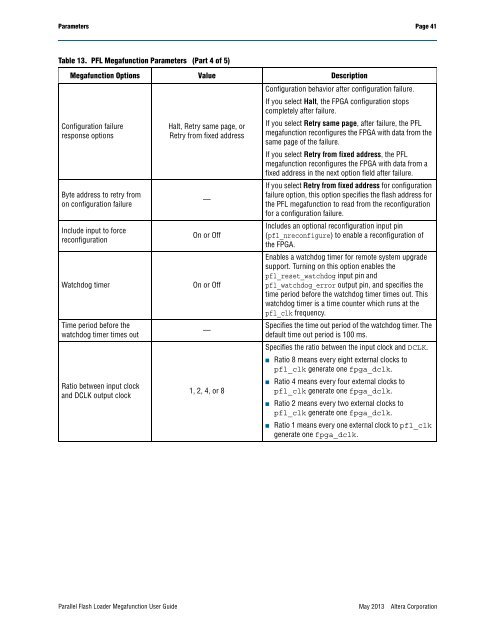

Table 13. PFL <strong>Megafunction</strong> Parameters (Part 4 of 5)<br />

<strong>Megafunction</strong> Options Value Description<br />

Configuration failure<br />

response options<br />

Byte address to retry from<br />

on configuration failure<br />

Include input to force<br />

reconfiguration<br />

Watchdog timer<br />

Time period before the<br />

watchdog timer times out<br />

Ratio between input clock<br />

and DCLK output clock<br />

Halt, Retry same page, or<br />

Retry from fixed address<br />

—<br />

On or Off<br />

On or Off<br />

—<br />

1, 2, 4, or 8<br />

Configuration behavior after configuration failure.<br />

If you select Halt, the FPGA configuration stops<br />

completely after failure.<br />

If you select Retry same page, after failure, the PFL<br />

megafunction reconfigures the FPGA with data from the<br />

same page of the failure.<br />

If you select Retry from fixed address, the PFL<br />

megafunction reconfigures the FPGA with data from a<br />

fixed address in the next option field after failure.<br />

If you select Retry from fixed address for configuration<br />

failure option, this option specifies the flash address for<br />

the PFL megafunction to read from the reconfiguration<br />

for a configuration failure.<br />

Includes an optional reconfiguration input pin<br />

(pfl_nreconfigure) to enable a reconfiguration of<br />

the FPGA.<br />

Enables a watchdog timer for remote system upgrade<br />

support. Turning on this option enables the<br />

pfl_reset_watchdog input pin and<br />

pfl_watchdog_error output pin, and specifies the<br />

time period before the watchdog timer times out. This<br />

watchdog timer is a time counter which runs at the<br />

pfl_clk frequency.<br />

Specifies the time out period of the watchdog timer. The<br />

default time out period is 100 ms.<br />

Specifies the ratio between the input clock and DCLK.<br />

■<br />

■<br />

■<br />

■<br />

Ratio 8 means every eight external clocks to<br />

pfl_clk generate one fpga_dclk.<br />

Ratio 4 means every four external clocks to<br />

pfl_clk generate one fpga_dclk.<br />

Ratio 2 means every two external clocks to<br />

pfl_clk generate one fpga_dclk.<br />

Ratio 1 means every one external clock to pfl_clk<br />

generate one fpga_dclk.<br />

<strong>Parallel</strong> <strong>Flash</strong> <strong>Loader</strong> <strong>Megafunction</strong> <strong>User</strong> <strong>Guide</strong><br />

May 2013<br />

<strong>Altera</strong> Corporation