Parallel Flash Loader Megafunction User Guide (PDF) - Altera

Parallel Flash Loader Megafunction User Guide (PDF) - Altera

Parallel Flash Loader Megafunction User Guide (PDF) - Altera

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Page 16<br />

Functional Description<br />

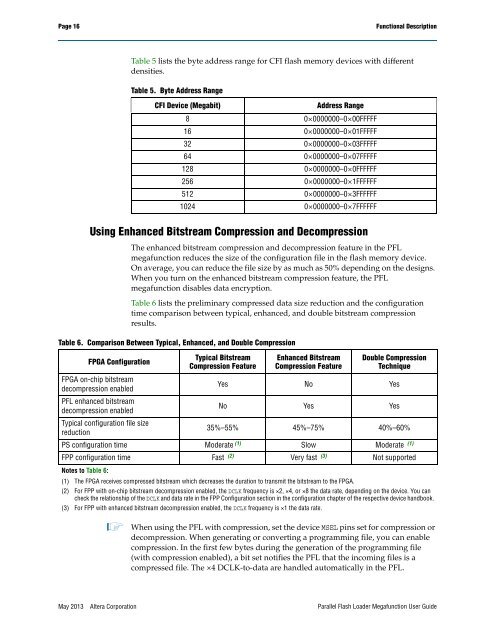

Table 5 lists the byte address range for CFI flash memory devices with different<br />

densities.<br />

Table 5. Byte Address Range<br />

CFI Device (Megabit)<br />

Address Range<br />

8 0×0000000–0×00FFFFF<br />

16 0×0000000–0×01FFFFF<br />

32 0×0000000–0×03FFFFF<br />

64 0×0000000–0×07FFFFF<br />

128 0×0000000–0×0FFFFFF<br />

256 0×0000000–0×1FFFFFF<br />

512 0×0000000–0×3FFFFFF<br />

1024 0×0000000–0×7FFFFFF<br />

Using Enhanced Bitstream Compression and Decompression<br />

The enhanced bitstream compression and decompression feature in the PFL<br />

megafunction reduces the size of the configuration file in the flash memory device.<br />

On average, you can reduce the file size by as much as 50% depending on the designs.<br />

When you turn on the enhanced bitstream compression feature, the PFL<br />

megafunction disables data encryption.<br />

Table 6 lists the preliminary compressed data size reduction and the configuration<br />

time comparison between typical, enhanced, and double bitstream compression<br />

results.<br />

Table 6. Comparison Between Typical, Enhanced, and Double Compression<br />

FPGA Configuration<br />

Typical Bitstream<br />

Compression Feature<br />

Enhanced Bitstream<br />

Compression Feature<br />

Double Compression<br />

Technique<br />

FPGA on-chip bitstream<br />

decompression enabled<br />

Yes No Yes<br />

PFL enhanced bitstream<br />

decompression enabled<br />

No Yes Yes<br />

Typical configuration file size<br />

reduction<br />

35%–55% 45%–75% 40%–60%<br />

PS configuration time Moderate (1) Slow Moderate (1)<br />

FPP configuration time Fast (2) Very fast (3) Not supported<br />

Notes to Table 6:<br />

(1) The FPGA receives compressed bitstream which decreases the duration to transmit the bitstream to the FPGA.<br />

(2) For FPP with on-chip bitstream decompression enabled, the DCLK frequency is ×2, ×4, or ×8 the data rate, depending on the device. You can<br />

check the relationship of the DCLK and data rate in the FPP Configuration section in the configuration chapter of the respective device handbook.<br />

(3) For FPP with enhanced bitstream decompression enabled, the DCLK frequency is ×1 the data rate.<br />

1 When using the PFL with compression, set the device MSEL pins set for compression or<br />

decompression. When generating or converting a programming file, you can enable<br />

compression. In the first few bytes during the generation of the programming file<br />

(with compression enabled), a bit set notifies the PFL that the incoming files is a<br />

compressed file. The ×4 DCLK-to-data are handled automatically in the PFL.<br />

May 2013 <strong>Altera</strong> Corporation <strong>Parallel</strong> <strong>Flash</strong> <strong>Loader</strong> <strong>Megafunction</strong> <strong>User</strong> <strong>Guide</strong>